### SUMMARY

- Circuits are important in electrical engineering because they process signals that carry energy and information. A **circuit** is an interconnection of electrical devices. A **signal** is an electrical current or voltage that carries energy or information. An **interface** is a pair of accessible terminals at which signals may be observed or specified.

- This book defines overall course objectives at the analysis, design, and evaluation levels. In **circuit analysis** the circuit and input signals are given and the object is to find the output signals. The object of **circuit design** is to devise one or more circuits that produce prescribed output signals for given input signals. The **evaluation** problem involves appraising alternative circuit designs using criteria such as cost, power consumption, and parts count.

- Charge (q) and energy (w) are the basic physical variables involved in electrical phenomena. Current (i), voltage (v), and power (p) are the derived variables used in circuit analysis and design. In the SI system, charge is measured in coulombs (C), energy in joules (J), current in amperes (A), voltage in volts (V), and power in watts (W).

- Current is defined as dq/dt and is a measure of the flow of electrical charge. Voltage is defined as dw/dq and is a measure of the energy required to move a small charge from one point to another. Power is defined as dw/dt and is a measure of the rate at which energy is being transferred. Power is related to current and voltage as p = vi.

- The reference marks (arrows and plus/minus signs) assigned to a device are reference directions, not indications of the way a circuit responds. The actual direction of the response is determined by comparing the reference direction and the algebraic sign of the answer found by circuit analysis using physical laws.

- Under the **passive sign convention**, the current reference arrow is directed toward the terminal with the positive voltage reference mark. Under this convention, the device power is positive when it absorbs power and is negative when it delivers power. When current and voltage have the same (opposite) algebraic signs, the device is absorbing (delivering) power.

## PROBLEMS

#### ERO 1-1 ELECTRICAL SYMBOLS AND UNITS (SECT. 1-2)

Given an electrical quantity described in terms of words, scientific notation, or decimal prefix notation, convert the quantity to an alternate description.

See Exercise 1–1

- 1-1 Write the following statements in symbolic form:

- (a) twelve milliamps

- (b) four hundred fifty five kilohertz

- (c) two hundred picoseconds

- (d) five megawatts

- 1-2 Express the following quantities using appropriate engineering prefixes (i.e., state the numeric to the nearest standard prefix).

- (a) 0.022 volts

- **(b)**  $23 \times 10^{-9}$  farads

- (c) 56,000 ohms

- (d)  $7.52 \times 10^5$  joules

- (e) 0.000235 henrys

- 1-3 An ampere-hour (Ah) meter measures the time-integral of the current in a conductor. During an 8-hour period a certain meter records 3300 Ah. Find the number of coulombs that flowed through the meter during the recording period.

- 1—4 Commercial electrical power companies measure energy consumption in kilowatt-hours, denoted kWh. One kilowatt-hour is the amount of energy transferred by 1 kW of power in a time period of 1 hour. During a one-month time period, a power company billing statement reports a user's total energy usage to be 2128 kWh. Determine the number of joules used during the billing period.

- 1-5 Fill in the blanks in the following statements.

- (a) To convert capacitance from microfarads to picofarads, multiply by \_\_\_\_\_.

- **(b)** To convert resistance from kilohms to megohms, multiply by \_\_\_\_\_\_.

- (c) To convert current from amperes to milliamperes, multiply by \_\_\_\_\_.

- (d) To convert power from watts to megawatts, multiply by \_\_\_\_\_.

#### ERO 1-2 CIRCUIT VARIABLES (SECT. 1-3)

Given any two of the three signal variables (i, v, p) or the two basic variables (q, w), find the magnitude and direction (sign) of the unspecified variables.

See Examples 1–1, 1–2, 1–3 and Exercises 1–1, 1–2, 1–3

- 1-6 The charge flowing through a device is q(t) = 3t 2 mC. Find the current through the device.

- 1-7 The charge flowing through a device is  $q(t) = 20e^{-3t}$   $\mu$ C. Find the current through the device.

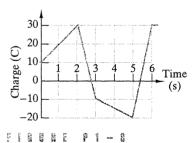

- Figure P1–8 shows a plot of the net positive charge flowing in a wire versus time. Sketch the corresponding current during the same time period.

- The current through a device is  $i(t) = 3t^2$  A. Find the total charge that flowed through the device between t = 0 and t = 2 s.

- 1–10 The current through a device is  $i(t) = 3e^{-2t}$  A. Find the total charge that flowed through the device between t = 0 and t = 0.1 s.

- For  $t \le 5$  s the current through a device is i(t) = 10 A. For  $5 < t \le 10$  s the current is i(t) = 20 - 2t A, and it is zero for t > 10. Sketch i(t) versus time and find the total charge through the device between t = 0 s and t = 10 s.

- 1-12 The charge flowing through a device is  $q(t) = 1 e^{-2000t} \mu C$ . Sketch the current through the device versus time for t > 0.

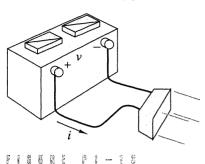

- The 12-V automobile battery in Figure P1-13 has an output capacity of 200 ampere-hours (Ah) when connected to a headlamp that absorbs 50 watts of power. Assume that the battery voltage is constant.

- (a) Find the current supplied by the battery.

- **(b)** How long can the battery power the headlight?

- An incandescent lamp absorbs 75 W when connected to a 120-V source.

- (a) Find the current through the lamp.

- **(b)** Find the cost of operating the lamp for 8 hours when electricity costs 6.8 cents/kW-hr.

- A total charge of 50 ampere-hours is supplied to a 12-V battery during recharging. Determine the number of joules supplied to the battery. Assume that battery voltage is constant.

- The voltage across a device is 25 V when the current through the device is  $i(t) = 3e^{-2t}$  A. Find the total energy delivered to the device between t = 0 and t = 0.5 s.

- When illuminated the i-v relationship for a photocell is  $i = e^{v} 10$  A. Calculate the device power and state whether the device is absorbing or delivering power when v = -3 V. Repeat for v = 1.5 V and 3 V.

- Using the passive sign convention, the current through and voltage across a two-terminal device are  $i = 1 2e^{-t}$  A and v = 25 V. Calculate the device power and state whether the device is absorbing or delivering power when t = 0.5 s, t = 1 s, and t = 10 s.

- The maximum power the device can dissipate is 0.25 W. Determine the maximum current allowed by the device power rating when the voltage is 50 V.

- 1-20 A laser produces 5-kW bursts of power that last 20 ns. If the burst rate is 40 bursts per second, what is the average power in the laser's output?

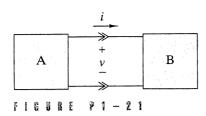

- 1-21 Two electrical devices are connected as shown in Figure P1-21. Using the reference marks shown in the figure, find the power transferred and state whether the power is transferred from A to B or B to A when

- (a) v = +33 V and i = -2.2 A

- **(b)** v = -12 V and i = -1.2 mA

- (c) v = +37.5 V and i = +40 mA

- **(d)** v = -15 V and i = -43 mA

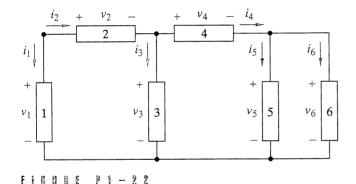

1-22 Figure P1-22 shows an electric circuit with a voltage and a current variable assigned to each of the six devices. The device signal variables are observed to be as follows:

Device 1,

$$v = 15$$

V,  $i = -1$  A, and  $p = ?$

Device 2,  $v = 5$  V,  $i = ?$ , and  $p = 5$  W

Device 3,  $v = ?$  V,  $i = 0.5$  A, and  $p = 5$  W

Device 4,  $v = 4$  V,  $i = 0.5$  A, and  $p = ?$

Device 5,  $v = ?$  V,  $i = 3$  A, and  $p = 18$  W

Device 6,  $v = ?$  V,  $i = -2.5$  A, and  $p = -15$  W

Find the unknown signal variable associated with each device and state whether the device is absorbing or delivering power. Use the power balance to check your work.

1-23 Figure P1-22 shows an electric circuit with a voltage and a current variable assigned to each of the six devices. The device signal variables are observed to be as follows:

Device 1,

$$v = 30$$

V,  $i = -2$  A, and  $p = ?$

Device 2,  $v = 10$  V,  $i = ?$ , and  $p = 20$  W

Device 3,  $v = 20$  V,  $i = ?$ , and  $p = 20$  W

Device 4,  $v = 8$  V,  $i = 1$  A, and  $p = ?$

Device 5,  $v = ?$  V,  $i = -5$  A, and  $p = -60$  W

Device 6,  $v = 12$  V,  $i = 6$  A, and  $p = ?$  W

Find the unknown signal variable associated with each device and state whether the device is absorbing or delivering power. Use the power balance to check your work.

- 1-24 Using the passive sign convention, the voltage across a device is  $v(t) = 5 \cos(10t)$  V and the current through the device  $i(t) = 0.5 \sin(10t)$  A. Calculate the device power at t = 0.2 s and t = 0.4 s and state whether the device is absorbing or delivering power.

- 1–25 For  $t \ge 0$  the voltage across and current through a device are  $v(t) = 10(1 - e^{-25t})$  V and  $i(t) = 0.5e^{-25t}$  A. Find the energy delivered to the device between t = 0 and t = 1 s.

# INTEGRATING PROBLEMS

#### 1-26 Power Ratio in dB

In complete darkness the voltage across and current through a two-terminal light detector are +5.6 V and +8 nA. In full sunlight the voltage and current are +0.9 V and +4 mA. Express the light/dark power ratio of the device in decibels (dB), where the power ratio in dB is

$$P_{dB} = 10 \log_{10} (p_2/p_1).$$

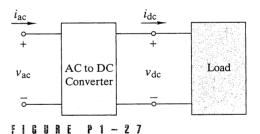

#### 1–27 AC to DC Converter

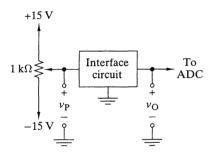

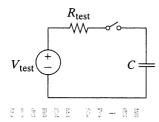

A manufacturer's data sheet for the converter in Figure P1-27 states that the AC input voltage is 120 V, the DC output is 24 V, and the efficiency is 82% when the output power is 200 W. Find the input and output currents.

# 1-28 Storage Battery Efficiency

The ampere-hour efficiency of a storage battery is the ratio of its ampere-hour output to the ampere-hour input required to recharge the battery. A certain 24-V battery has a rated output of 400 ampere-hours. When the battery is completely drained, a battery charger must deliver 75 A for 6 hours to recharge the battery. Assume that the battery voltage is constant.

- (a) Determine the ampere-hour efficiency of the battery.

- (b) Determine the number of joules required to recharge the battery.

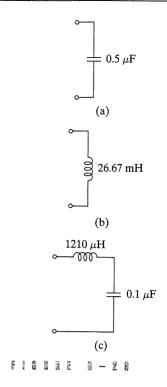

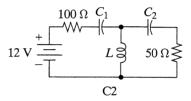

FIGURE 2-81

#### SUMMARY

- An **electrical device** is a real physical entity, while a **circuit element** is a mathematical or graphical model that approximates major features of the device.

- Two-terminal circuit elements are represented by a circuit symbol and are characterized by a single constraint imposed on the associated current and voltage variables.

- An **electrical circuit** is an interconnection of electrical devices. The interconnections form nodes and loops.

- A **node** is an electrical juncture of the terminals of two or more devices. A **loop** is a closed path formed by tracing through a sequence of devices without passing through any node more than once.

- Device interconnections in a circuit lead to two connection constraints: **Kirchhoff's current law (KCL)** states that the algebraic sum of currents at a node is zero at every instant; and **Kirchhoff's voltage law (KVL)** states that the algebraic sum of voltages around any loop is zero at every instant.

- A pair of two-terminal elements are connected in **parallel** if they form a loop containing no other elements. The same voltage appears across any two elements connected in parallel.

- A pair of two-terminal elements are connected in **series** if they are connected at a node to which no other elements are connected. The same current exists in any two elements connected in series.

- Two circuits are said to be **equivalent** if they each have the same *i*–*v* constraints at a specified pair of terminals.

- Series and parallel equivalence and voltage and current division are important tools in circuit analysis and design.

- Source transformation changes a voltage source in series with a resistor into an equivalent current source in parallel with a resistor, or vice versa.

- Circuit reduction is a method of solving for selected signal variables in ladder circuits. The method involves sequential application of the series/parallel equivalence rules, source transformations, and the voltage/current division rules. The reduction sequence used depends on the variables to be determined and the structure of the circuit and is not unique.

# PROBLEMS

#### ERO 2-1 ELEMENT CONSTRAINTS (SECT. 2-1)

Given a two-terminal element with one or more electrical variables specified, use the element i– $\nu$  constraint to find the magnitude and direction of the unknown variables. See Example 2–1

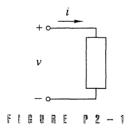

- 2-1 Figure P2-1 shows a general two-terminal element with voltage and current reference marks assigned. Find the unknown electrical variables when the element is:

- (a) A linear 5-k $\Omega$  resistor with  $\nu = 50$  V.

- **(b)** An ideal 10-mA current source with the arrow directed upward and p = 30 mW.

- 2–2 Figure P2–1 shows a general two-terminal element. Determine as much as you can about the element value and signal variables when the element is:

- (a) An ideal 15-V voltage source with the plus terminal at the top and i = 5 mA.

- **(b)** An ideal switch with i = 20 A.

- 2-3 When the voltage across a linear resistor is 12 V the current is 3 mA. Find the conductance of the resistor.

- 2-4 The design guidelines for a circuit call for using only \(^1\)4-W resistors. The maximum voltage level in the circuit is known to be 12 V. Determine the smallest allowable value of resistance.

- 2-5 The i- $\nu$  measurements for an unknown element are as follows: i = 7.5 mA @  $\nu = 15$  V, i = 4.3 mA @  $\nu = 8.6$  V, i = -4 mA @  $\nu = -8$  V. Use these measurements to estimate the current through the element when  $\nu = -15$  V. Is the device linear?

- 2-6 The i- $\nu$  relationship of a nonlinear resistor is  $\nu = 75i$   $+ 0.2i^3$ .

- (a) Calculate v and p for  $i = \pm 0.5, \pm 1, \pm 2, \pm 5$ , and  $\pm 10$  A. (b) If the operating range of the device is limited to |i|

- (b) If the operating range of the device is limited to |i| < 0.5 A, what is the maximum error in ν when the device is approximated by a 75-Ω linear resistance?</p>

- 2–7 A certain 10-k $\Omega$  resistor dissipates 12 mW. Find the current through the device.

- 2–8 A certain type of film resistor is available with resistance values between 10  $\Omega$  and 100 M $\Omega$ . The maximum ratings for all resistors of this type are 400 V and ½ W. Show that the voltage rating is the controlling limit when  $R > 320 \text{ k}\Omega$ , and that the power rating is the controlling limit when  $R < 320 \text{ k}\Omega$ .

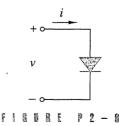

- Figure P2-9 shows the circuit symbol for a class of two-terminal devices called diodes. The  $i-\nu$  relationship for a p-n junction diode is

$$i = 2 \times 10^{-16} (e^{40 v} - 1)$$

(a) Use this equation to find i and p for  $v = 0, \pm 0.1$ ,  $\pm 0.2$ ,  $\pm 0.4$ , and  $\pm 0.8$  V. Use these data to plot the i- $\nu$  characteristic of the element.

- **(b)** Is the diode linear or nonlinear, bilateral or nonbilateral, and active or passive?

- (c) Use the diode model to predict i and p for v = 5 V. Do you think the model applies to voltages in this range? Explain.

- (d) Repeat (c) for v = -5 V.

- 2-10 The resistance of a device is given by

$$R = 0.3T_C + 100$$

where  $T_{\rm C}$  is the device temperature in degrees Celsius. Find the voltage across the device when the current is 1 mA and the temperature is 400°C.

## ERO 2-2 CONNECTION CONSTRAINTS (SECT. 2-2)

Given a circuit composed of two-terminal elements:

- (a) Identify nodes and loops in the circuit.

- (b) Identify elements connected in series and in parallel.

- (c) Use Kirchhoff's laws (KCL and KVL) to find selected signal variables.

See Examples 2-4, 2-5, 2-6 and Exercises 2-1, 2-2, 2-3, 2-4, 2-5

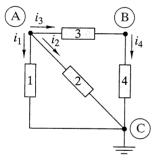

- 2–11 For the circuit in Figure P2–11,

- (a) Identify the nodes and at least two loops.

- (b) Identify any elements connected in series or in parallel.

- (c) Write KCL and KVL connection equations for the circuit.

- (d) If  $i_1 = 6$  mA and  $i_2 = -4$  mA, find the other element currents.

FIGURE P2-11

- 2-12 The currents in Figure P2-11 are observed to be  $i_1 = 20$  mA and  $i_3 = -30$  mA. Find the other element currents in the circuit.

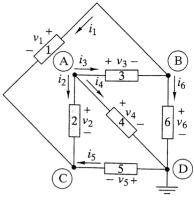

- 2–13 For the circuit in Figure P2–13,

- (a) Identify the nodes and at least three loops in the circuit.

- (b) Identify any elements connected in series or in parallel.

- (c) Write KCL and KVL connection equations for the circuit.

(d) If  $v_3 = -8$  V,  $v_4 = -8$  V, and  $v_5 = 9$  V, find the other element voltages.

FIGURE P2-13

- **2–14** In Figure P2–13  $v_1 = -8$  V,  $v_4 = 8$  V, and  $v_6 = 6$  V. Find the other element voltages.

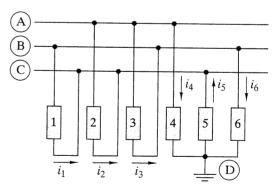

- 2–15 The circuit in Figure P2–15 is organized around the three signal lines A, B, and C.

- (a) Identify the nodes and at least three loops in the circuit.

- (b) Write KCL connection equations for the circuit.

- (c) If  $i_3 = 15$  mA,  $i_4 = -12$  mA, and  $i_5 = 5$  mA, find the other element currents.

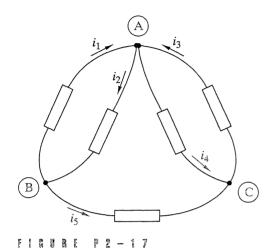

FIGURE P2-15

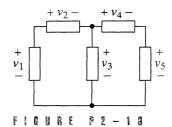

- **2–16** In Figure P2–16  $v_1 = 5 \text{ V}$ ,  $v_3 = -10 \text{ V}$ , and  $v_4 = 10 \text{ V}$ . Find  $v_2$  and  $v_5$ .

- **2–17** In the circuit in Figure P2–17  $i_1 = 2$  A,  $i_2 = -5$  A, and  $i_3 = 4$  A. Use KCL to find  $i_4$  and  $i_5$ .

60 CHAPTER S

2-18 The connection equations for a certain circuit are

$$\begin{array}{c} v_1 - v_2 - v_3 = 0 \\ v_3 + v_4 + v_5 = 0 \end{array} \qquad \begin{array}{c} i_1 + i_2 = 0 \\ -i_2 + i_3 - i_4 = 0 \\ i_4 - i_5 = 0 \\ -i_1 - i_3 + i_5 = 0 \end{array}$$

Draw the circuit diagram and indicate the reference marks for the element voltages and currents.

2-19 The incident matrix  $A = [a_{ij}]$  of a circuit has one row for each node and one column for each element. If the *j*th element is not connected to the *i*th node, then  $a_{ij} = 0$ . If the *j*th element is connected to the *i*th node, then  $a_{ij} = \pm 1$ , where the plus sign applies if the current reference direction is into the node and the minus sign applies if it is away from the node. The incident matrix of a circuit is

$$A = \begin{bmatrix} -1 & +1 & 0 & -1 & 0 \\ 0 & -1 & -1 & 0 & +1 \\ +1 & 0 & +1 & +1 & -1 \end{bmatrix}$$

Draw the circuit diagram and indicate the reference directions for currents and voltages using the passive sign convention.

2–20 Given the definition in Problem 2–19, construct the incident matrix for the circuit corresponding to the connection equations in Problem 2–18.

## ERO 2-3 COMBINED CONSTRAINTS (SECT. 2-3)

Given a circuit consisting of independent sources and linear resistors, use the element constraints and connection constraints to find selected signal variables.

See Examples 2-7, 2-8, 2-9, 2-10 and Exercise 2-6

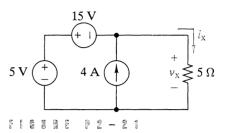

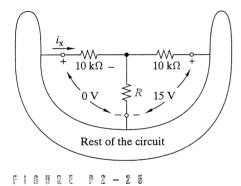

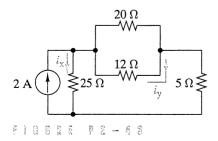

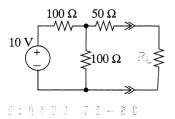

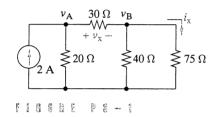

2-21 Find  $v_x$  and  $i_x$  in Figure P2-21.

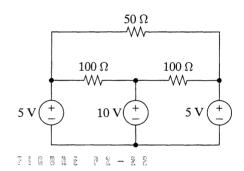

2-22 First use KVL to find the voltage across each resistor in Figure P2-22. Then use Ohm's law and KCL to find the current through every element, including the voltage sources.

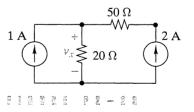

2-23 Find  $v_x$  in Figure P2-23.

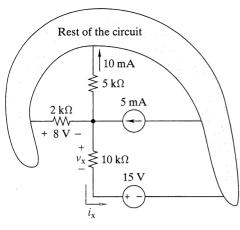

- Figure P2-24 shows a subcircuit connected to the rest of the circuit at four points.

- (a) Use element and connection constraints to find  $v_x$  and  $i_x$ .

- (b) Show that the sum of the currents into the rest of the circuit is zero.

FIRHRE P2-24

2-25 The circuit in Figure P2-25 is a model of the feedback path in an electronic amplifier circuit. The current  $i_x$  is known to be 4 mA. (a) Find the value of R. (b) Show that the sum of currents into the rest of the circuit is zero.

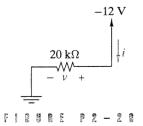

2–26 Figure P2–26 shows a resistor with one terminal connected to ground and the other connected to an arrow. The arrow symbol is used to indicate a connection to one terminal of a voltage source whose other terminal is connected to ground. The label next to the arrow indicates the source voltage at the ungrounded terminal. Find the voltage across, current through, and power dissipated in the resistor.

#### ERO 2-4 EQUIVALENT CIRCUITS (SECT. 2-4)

- (a) Given a circuit consisting of linear resistors, find the equivalent resistance between a specified pair of terminals.

- (b) Given a circuit consisting of a source-resistor combination, find an equivalent source-resistor circuit.

See Example 2-11, 2-12 and Exercises 2-7, 2-8, 2-9

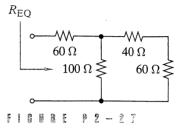

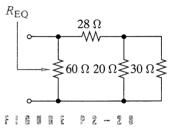

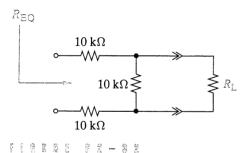

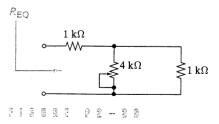

2–27 Find the equivalent resistance  $R_{EO}$  in Figure P2–27.

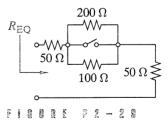

2-28 Find the equivalent resistance  $R_{EO}$  in Figure P2-28.

2-29 Find the equivalent resistance  $R_{\rm EQ}$  in Figure P2-29 when the switch is open. Repeat when the switch closed.

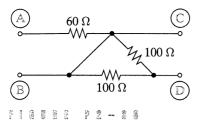

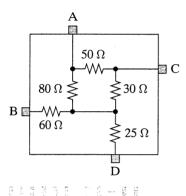

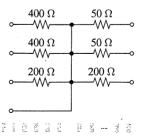

- 2-30 Find the equivalent resistance between terminals A-B, B-C, A-C, C-D, B-D, and A-D in the circuit of Figure P2-30.

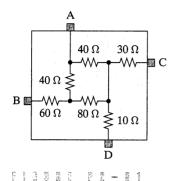

- 2-31 Find the equivalent resistance between terminals A-B, A-C, A-D, B-C, B-D, and C-D in the circuit of Figure P2-31.

62

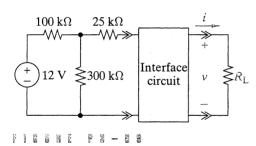

2-32 Find the equivalent resistance  $R_{\rm EQ}$  in Figure P2-32 when  $R_{\rm L}=10~{\rm k}\Omega$ . Repeat when  $R_{\rm L}=0$ . Select the value of  $R_{\rm L}$  so that  $R_{\rm EQ}=22~{\rm k}\Omega$ .

- An ideal 15-V voltage source is connected in series with a 50- $\Omega$  resistor. Use source transformations to obtain an equivalent practical current source.

- A 5-mA practical current source is connected in parallel with a  $2-k\Omega$  resistor. The voltage across the resistor is observed to be 5 V. Find the source resistance of the practical current source.

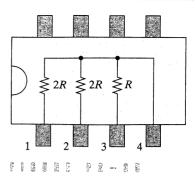

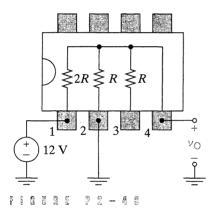

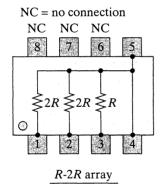

- The circuit of Figure P2-35 is an R-2R resistance array package. All of the following equivalent resistances can be obtained by making proper connections of the array except for one: R/2, 2R/3, R, 8R/5, 2R, 3R, and 4R. Show how to interconnect the terminals of the array to produce the equivalent resistances, and identify the one that cannot be obtained using this array.

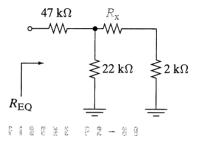

2-36 Select the value of  $R_x$  in Figure P2-36 so that  $R_{EQ} = 49 \text{ k}\Omega$ .

- 2-37 Using no more than 14 resistors, show how to interconnect standard 4.3-kΩ resistors to obtain equivalent resistances of 1 kΩ ±10%, 5 kΩ ±10%, and 10 kΩ ±10%.

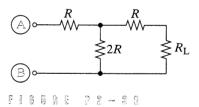

- Select the value of R in Figure P2-38 so that  $R_{AB} = R_{L}$ .

2-39 What is the range of  $R_{EQ}$  in Figure P2-39?

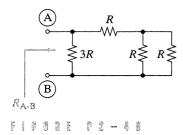

Find the equivalent resistance between terminals A and B in Figure P2-40.

# ERO 2-5 VOLTAGE AND CURRENT DIVISION (SECT. 2-5)

- (a) Given a circuit with elements connected in series or parallel, use voltage or current division to find specified voltages or currents.

- (b) Design a voltage or current divider that delivers specified output signals within stated constraints.

- See Examples 2-13, 2-14, 2-16, 2-17, 2-18 and Exercises 2-10, 2-11, 2-12

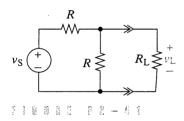

- Use voltage division in Figure P2-41 to obtain an expression for  $v_L$  in terms of R,  $R_L$ , and  $v_S$ .

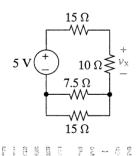

2-42 Find  $v_x$  in Figure P2-42.

2-43 Find  $i_x$  in Figure P2-43.

- 2-44 Find  $i_v$  in Figure P2-43.

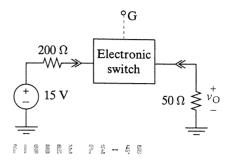

- The electronic switch in Figure P2-45 is controlled by the voltage between gate G and ground. The switch is closed ( $R_{\rm ON}=100~\Omega$ ) when  $\nu_{\rm G}>2~{\rm V}$  and open ( $R_{\rm OFF}=500~{\rm M}\Omega$ ) when  $\nu_{\rm G}<0.8~{\rm V}$ . Use voltage division to predict  $\nu_{\rm O}$  when  $\nu_{\rm G}=5~{\rm V}$  and  $\nu_{\rm G}=0.5~{\rm V}$ .

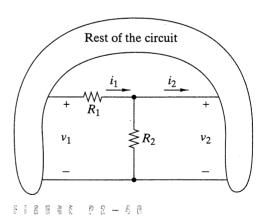

- Figure P2-46 shows a resistance divider connected in a general circuit.

- (a) What is the relationship between  $v_1$  and  $v_2$  when  $i_1 = 0$ ?

- **(b)** What is the relationship between  $v_1$  and  $v_2$  when  $i_2 = 0$ ?

- (c) What is the relationship between  $i_1$  and  $i_2$  when  $v_1 = 0$ ?

- (d) What is the relationship between  $i_1$  and  $i_2$  when  $v_2 = 0$ ?

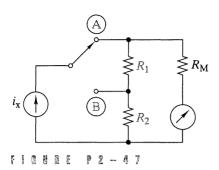

Figure P2-47 shows an ammeter circuit consisting of a D'Arsonval meter, a two-position selector switch, and two shunt resistors. A current of 0.5 mA produces full-scale deflection of the D'Arsonval meter, whose internal resistance is  $R_{\rm M} = 50~\Omega$ . Select the shunt resistance  $R_{\rm 1}$  and  $R_{\rm 2}$  so that  $i_{\rm x} = 10$  mA produces full scale deflection when the switch is in position A, and  $i_{\rm x}$

= 50 mA produces full-scale deflection when the switch is in position B.

2-48 Figure P2-48 shows the R-2R integrated circuit package connected as a voltage divider and across a 15-V source. The divider output is 5 V for the connections shown in the figure. Show how to interconnect the source and the R-2R package to obtain outputs of 3 V, 6 V, 9 V, and 12 V.

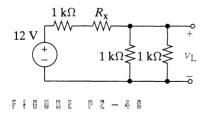

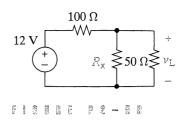

2-49 Find the value of  $R_x$  in Figure P2-49 such that  $v_L = 2 \text{ V}$ .

2-50 Find the value of  $R_x$  in Figure P2-50 such that  $v_L = 3 \text{ V}$ .

#### ERO 2-6 CIRCUIT REDUCTION (SECT. 2-6)

Given a circuit consisting of linear resistors and an independent source, find selected signal variables using successive application of series/parallel equivalence, source transformations, and voltage/current division.

See Example  $\tilde{2}$ –20, 2–21, 2–22, 2–23 and Exercises 2–13, 2–14, 2–15

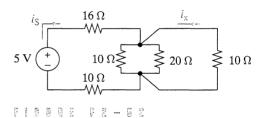

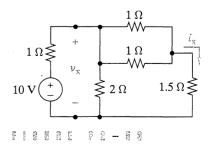

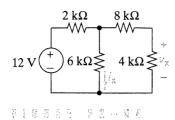

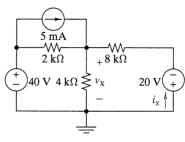

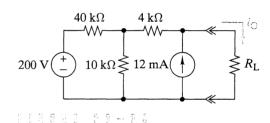

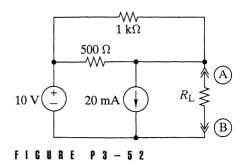

2-5] Use circuit reduction to determine  $v_x$  and  $i_x$  in the circuit shown in Figure P2-51.

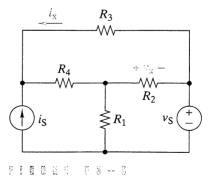

2-52 Use circuit reduction to find  $i_s$  and  $i_x$  in the circuit shown in Figure P2-52.

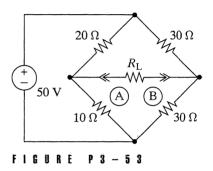

2-53 Use circuit reduction to find  $v_x$  and  $i_x$  in the circuit shown in Figure P2-53.

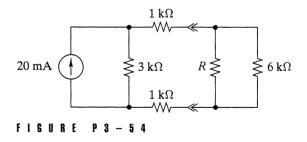

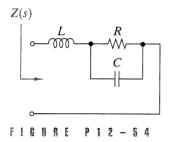

2-54 Use circuit reduction to find  $v_x$  and  $i_x$  in the circuit shown in Figure P2-54.

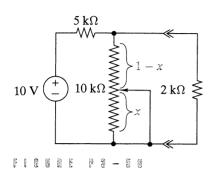

The resistance array circuit in Figure P2-55 has external terminals at pads A, B, C, and D. Connect the "+" terminal of a 10-V voltage to terminal A and the "-" to terminal C. Find the voltage  $v_{AB}$ .

- 7-55 The resistance array circuit in Figure P2-55 has external terminals at pads A, B, C, and D. Connect the "+" terminal of a 10-V voltage to terminal A and the "-" to terminal B. Find the voltage  $v_{\rm DB}$ .

- The resistance array circuit in Figure P2-55 has external terminals at pads A, B, C, and D. Connect the "+" terminal of a 5-V voltage to terminal C and the "-" to ground. Connect terminal B to ground. Find the voltage  $v_{DB}$ .

- Select the value of  $R_L$  in Figure P2-58 so that the power delivered to  $R_L$  is at least 50 mW.

- Select the value of  $R_L$  in Figure P2–58 so that the voltage delivered to  $R_L$  is at least 2.5 V.

The box in the circuit in Figure P2-60 is a resistor whose value can be anywhere between  $8 \text{ k}\Omega$  and  $80 \text{ k}\Omega$ . Use circuit reduction to find the range of values of the outputs  $v_x$  and  $i_x$ .

# INTEGRATING PROBLEMS

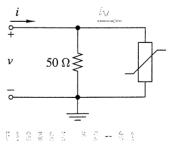

- Device Modeling

- The circuit in Figure P2–61 consists of a 50- $\Omega$  linear resistor in parallel with a nonlinear varistor whose  $i-\nu$  characteristic is  $i_V = 2.6 \times 10^{-5} v^3$ .

- (a) Plot the i-v characteristic of the parallel combination.

- (b) State whether the parallel combination is linear or nonlinear, active or passive, and bilateral or nonbilateral.

- (c) Identify a range of voltages over which the parallel combination can be modeled within ±10% by a linear resistor.

- (d) Identify a range of voltages over which the parallel combination can be safely operated if both devices are rated at 50 W. Which device limits this range?

- (e) The parallel combination is connected in series with a  $50-\Omega$  resistor and a 5-V voltage source. In this circuit, how would you model the parallel combination and why?

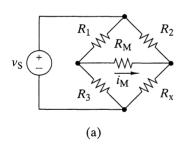

2-52 Wheatstone Bridge 🏰

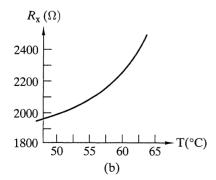

The Wheatstone bridge circuit in Figure P2-62(a) is used in instrumentation systems. The resistance  $R_x$  is

the equivalent resistance of a transducer (a device that converts energy from one form to another). The value of  $R_{\rm x}$  varies in relation to an external physical phenomenon such as temperature, pressure, or light. The resistance  $R_{\rm M}$  is the equivalent resistance of a measuring instrument such as a D'Arsonval meter. Prior to any measurements, one of the other resistors (usually  $R_{\rm 3}$ ) is adjusted until the current  $i_{\rm M}$  is zero. The resistance of the transducer changes when exposed to the physical phenomenon it is designed to measure. This change causes the bridge to become unbalanced, and the meter indicates the resulting current through  $R_{\rm M}$ . The deflection of the meter is calibrated to indicate the value of the physical phenomenon measured by the transducer.

- (a) Derive the relationship between  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_x$  when  $i_M = 0$  A.

- (b) Suppose the transducer resistance  $R_x$  varies with temperature, as shown in Figure P2-62(b). With  $R_1 = R_2 = 2.2 \text{ k}\Omega$ , find the value of  $R_3$  that produces  $i_M = 0$  at a temperature of 57.5° C.

- (c) A current  $i_{\rm M} = -1.5$  mA is observed when  $R_1 = R_2 = 2.2$  k $\Omega$  and  $R_3$  is set to the value found in part (b). Is the temperature higher or lower than 57.5° C?

- (d) A For  $R_1 = R_2 = 2.2 \text{ k}\Omega$  and  $R_3 = 2.4 \text{ k}\Omega$ , find the temperature at which  $i_M = 0$ .

FIGURE P2-62

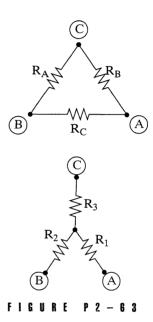

### 2-63 Three-Terminal Equivalence

Two circuits are said to be equivalent when they have the same i- $\nu$  characteristics between specified terminal pairs. In this chapter we applied this definition to two-terminal circuits such as resistors in series or parallel and source transformations. The concept can be extended to the three-terminal circuits in Figure P2–63. These three-terminal circuits will be equivalent if the equivalent resistances seen between terminal pairs A and B, B and C, and C and A are the same.

(a) A Show that the two circuits are equivalent when

$$R_1 = \frac{R_B R_C}{R_A + R_B + R_C} \text{ and}$$

$$R_2 = \frac{R_C R_A}{R_A + R_B + R_C} \text{ and}$$

$$R_3 = \frac{R_A R_B}{R_A + R_B + R_C}$$

(b) A Equivalence is useful because replacing one circuit by an equivalent circuit does not change the response of the rest of the circuit and may simplify an analysis problem. For example, the equations in (a) tell us how to create an equivalent Y-connected subcircuit like Figure P2–63(b) to replace the Δ-connected subcircuit in Figure P2–63(a). Such a replacement is called a Δ-to-Y transformation. Show that a Y-to-Δ transformation is also possible provided

$$G_{\rm A} = \frac{G_2 G_3}{G_1 + G_2 + G_3}$$

and  $G_{\rm B} = \frac{G_1 G_3}{G_1 + G_2 + G_3}$  and  $G_{\rm C} = \frac{G_1 G_2}{G_1 + G_2 + G_3}$

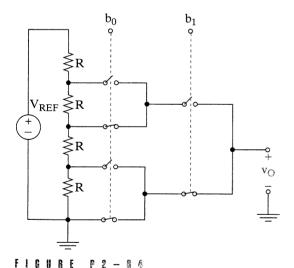

#### 2-64 Digital-to-Analog Conversion

Digital-to-analog (D-to-A) conversion provides a link between the digital and analog worlds. A D-to-A converter produces a single analog output  $v_0$  from a multibit digital input  $\{b_0, b_1, b_2, \ldots b_{N-1}\}$ , where the bits  $b_j$   $(j=0,1,\ldots N-1)$  are either 0 or 1. One method is to produce an analog output that is proportional to a fixed reference voltage  $V_{REF}$  and related to the digital inputs by the following algorithm

$$v_{\rm O} = KV_{\rm REF} \sum_{\rm i=0}^{\rm N-1} b_{\rm j} 2^{\rm j}$$

Figure P2–64 shows a programmable voltage divider in which two digital inputs control complementary analog switches connecting a multitap voltage divider to the output terminal. Show that the programmable voltage divider implements this D-to-A algorithm with K = 0.25 and N = 2.

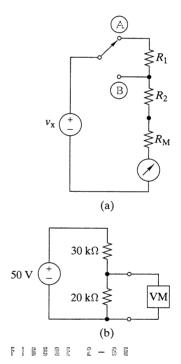

-65 Analog Voltmeter Design A voltmeter can be made

using a series resistor and a D'Arsonval meter. Figure P2-65(a) shows a voltmeter circuit consisting of a D'Arsonval meter, a two-position selector switch, and two series resistors. A current of 500  $\mu A$  produces full-

scale deflection of the D'Arsonval meter, whose internal registance is  $R_{\rm M}=50~\Omega$ .

- (a) Select the series resistance  $R_1$  and  $R_2$  so a voltage  $v_x = 50$  V produces full-scale deflection when the switch is in position A, and voltage  $v_x = 10$  V produces full-scale deflection when the switch is in position B.

- (b) By voltage division the voltage across the 20- $k\Omega$  resistor in Figure P2-65(b) is 20 V when the voltmeter is disconnected. What voltage reading is obtained when the voltmeter designed in part (a) is connected across the 20- $k\Omega$  resistor? What is the percentage error in the voltmeter reading?

- (c) A D'Arsonval meter with an internal resistance of 200 Ω and a full-scale deflection current of 100 μA is available. If the voltmeter in part (a) is redesigned using this D'Arsonval meter, would the error found in part (b) be smaller or larger? Explain.

DISCUSSION: (a) A standard 56- $\Omega$  resistor in series (ideally 58.1  $\Omega$ ) yields 200 mW ±5% into the 50- $\Omega$  load. (b) No resistive interface will work since the maximum power available from the source is only 0.5 W. Delivering more power than the signal source can provide requires an active device, such as an OP AMP or transistor (treated in the next chapter).

## SUMMARY

- $^{\circ}$  Node-voltage analysis involves identifying a reference node and the node to datum voltages at the remaining N-1 nodes. The KCL connection constraints at the N-1 nonreference nodes combined with the element constraints written in terms of the node voltages produce N-1 linear equations in the unknown node voltages.

- Mesh-current analysis involves identifying mesh currents that circulate around the perimeter of each mesh in a planar circuit. The KVL connection constraints around E-N+1 meshes combined with the element constraints written in terms of the mesh currents produce E-N+1 linear equations in the unknown mesh currents.

- Node and mesh analysis can be modified to handle both types of independent sources using a combination of three methods: (1) source transformations, (2) selecting circuit variables so independent sources specify the values of some of the unknowns, and (3) using supernodes or supermeshes.

- A circuit is linear if it contains only linear elements and independent sources. For single-input linear circuits, the proportionality property states that any output is proportional to the input. For multiple-input linear circuits, the superposition principle states that any output can be found by summing the output produced when each input acts alone.

- A Thévenin equivalent circuit consists of a voltage source in series with a resistance. A Norton equivalent circuit consists of a current source in parallel with a resistance. The Thévenin and Norton equivalent circuits are related by a source transformation.

- The parameters of the Thévenin and Norton equivalent circuits can be determined using any two of the following: (1) the open-circuit voltage at the interface, (2) the short-circuit current at the interface, and (3) the equivalent resistance of the source circuit with all sources turned off.

- The parameters of the Thévenin and Norton equivalent circuits can also be determined using circuit reduction methods or by directly solving for the source *i*–*v* relationship using node-voltage or mesh-current analysis.

- For a fixed source and an adjustable load, the maximum interface signal levels are  $v_{\rm MAX} = v_{\rm OC} \, (R_{\rm L} = \infty), \, i_{\rm MAX} = i_{\rm SC} \, (R_{\rm L} = 0), \, {\rm and} \, p_{\rm MAX} = v_{\rm OC} i_{\rm SC} / 4 \, (R_{\rm L} = R_{\rm T}).$  When  $R_{\rm L} = R_{\rm T}$ , the source and load are said to be matched.

- Interface signal transfer conditions are specified in terms of the voltage, current, or power delivered to the load. The design constraints depend on the signal conditions specified and the circuit parameters that are adjustable. Some design requirements may require a two-port interface circuit. An interface design problem may have one, many, or no solutions.

## **PROBLEMS**

# ERO 3-1 GENERAL CIRCUIT ANALYSIS (SECT. 3-1 to 3-2)

Given a circuit consisting of linear resistors and independent sources,

- (a) (Formulation) Write node-voltage or mesh-current equations for the circuit.

- (b) (Solution) Solve the equations from (a) for selected signal variables or input-output relationships.

Node-voltage method:

See Examples 3–1, 3–2, 3–3, 3–4, 3–5, 3–6 and Exercises 3–2, 3–3, 3–4, 3–5, 3–6

Mesh-current method:

See Examples 3-7, 3-8, 3-9, and Exercises 3-8, 3-9, 3-10

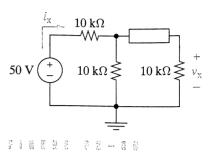

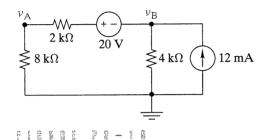

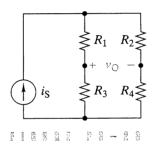

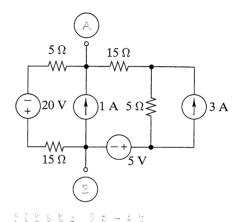

- 3-1 (a) Formulate node-voltage equations for the circuit in Figure P3-1.

- **(b)** Use these equations to find  $v_x$  and  $i_x$ .

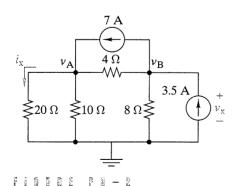

- 3-2 (a) Formulate node-voltage equations for the circuit in Figure P3-2.

- **(b)** Use these equations to find  $v_x$  and  $i_x$ .

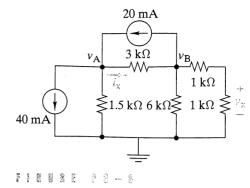

- 3-3 (a) Formulate node-voltage equations for the circuit in Figure P3-3.

- **(b)** Use these equations to find  $v_x$  and  $i_x$ .

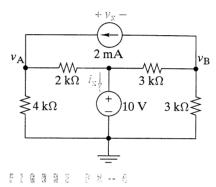

- (a) Formulate a set of node-voltage equations for the circuit in Figure P3-4.

- **(b)** Use these equations to find  $v_x$  and  $i_x$ .

- (a) Formulate node-voltage equations for the circuit in Figure P3-5.

- **(b)** Solve for  $v_x$  and  $i_x$  when  $v_S = 4$  V,  $i_S = 2$  mA,  $R_1 = R_2 = 10$  k $\Omega$ , and  $R_3 = R_4 = 5$  k $\Omega$ .

- (a) Formulate node-voltage equations for the circuit in Figure P3-6.

- **(b)** Solve for  $v_x$  and  $i_x$  using  $R_1 = 10 \text{ k}\Omega$ ,  $R_2 = 10 \text{ k}\Omega$ ,  $R_3 = 40 \text{ k}\Omega$ ,  $R_4 = 20 \text{ k}\Omega$ ,  $v_1 = v_2 = 5 \text{ V}$ , and  $v_3 = 15 \text{ V}$ .

- (c) Find the power delivered to resistor  $R_1$ .

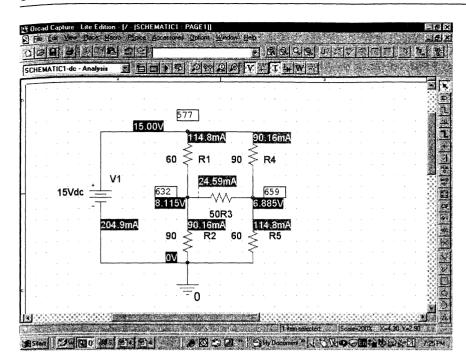

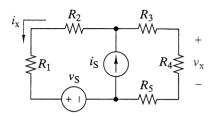

- 3-12 (a) Formulate mesh-current equations for the circuit in Figure P3-12.

- **(b)** Solve for  $v_x$  and  $i_x$  using  $R_1 = 200 \ \Omega$ ,  $R_2 = 500 \ \Omega$ ,  $R_3 = 60 \ \Omega$ ,  $R_4 = 240 \ \Omega$ ,  $R_5 = 200 \ \Omega$ ,  $i_S = 50 \ \text{mA}$ , and  $v_S = 15 \ \text{V}$ .

- (c) Find the total power dissipated in the circuit.

FIGURE P3-12

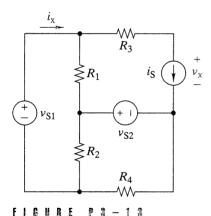

- 3-13 (a) Formulate mesh-current equations for the circuit in Figure P3-13.

- **(b)** Solve for  $v_x$  and  $i_x$  using  $R_1 = R_2 = 10 \text{ k}\Omega$ ,  $R_3 = 2 \text{ k}\Omega$ ,  $R_4 = 1 \text{ k}\Omega$ ,  $i_S = 2.5 \text{ mA}$ ,  $v_{S1} = 12 \text{ V}$ , and  $v_{S2} = 0.5 \text{ V}$

- (c) Find the power supplied by  $v_{S1}$ .

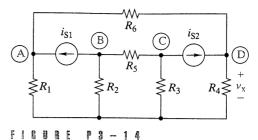

- 3-14 The circuit in Figure P3-14 seems to require two supermeshes since both current sources appear in two meshes. However, a circuit diagram can sometimes be rearranged to eliminate the need for supermesh equations.

- (a) Show that supermeshes in Figure P3-14 can be avoided by connecting resistor  $R_6$  between node A and node D via a different route.

- **(b)** Formulate mesh-current equations for the modified circuit as redrawn in (a).

- (c) Solve for  $v_x$  using  $R_1 = R_2 = R_3 = R_4 = 2 \text{ k}\Omega$ ,  $R_5 = R_6 = 1 \text{ k}\Omega$ ,  $i_{S1} = 40 \text{ mA}$ , and  $i_{S2} = 20 \text{ mA}$ .

- 3-15 (a) Formulate mesh-current equations for the circuit in Figure P3-15.

- **(b)** Use these equations to find  $v_x$  and  $i_x$ .

- (c) Find the total power delivered to the resistors.

FIGURE P3-15

- 3-16 (a) Formulate mesh-current equations for the circuit in Figure P3-16.

- (b) Use these equations to find the input resistance.

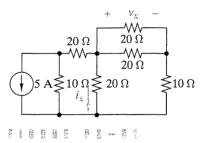

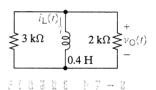

-17 Use node-voltage or mesh-current analysis to find  $i_x$  in Figure P3–17.

FIGURE P3-17

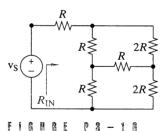

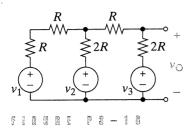

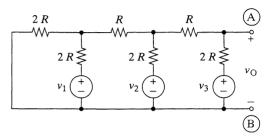

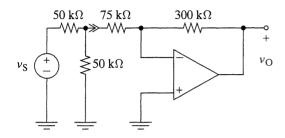

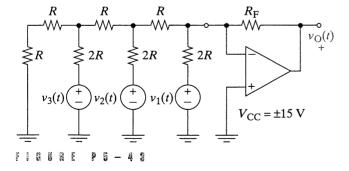

Use the node-voltage or mesh-current method in Figure P3–18 to find  $v_0$  in terms of  $v_1$ ,  $v_2$ , and  $v_3$ .

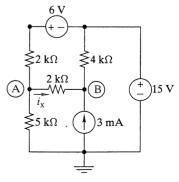

Find the node voltages  $v_A$  and  $v_B$  in Figure P3-19.

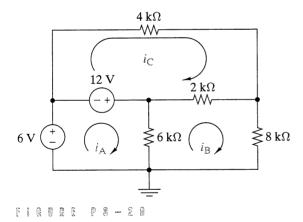

3-20 Find the mesh currents  $i_A$ ,  $i_B$ , and  $i_C$  in Figure P3–20.

## ERO 3-2 LINEARITY PROPERTIES (SECT. 3-3)

- (a) Given a circuit containing linear resistors and one independent source, use the proportionality principle to find selected signal variables.

- (b) Given a circuit containing linear resistors and two or more independent sources, use the superposition principle to find selected signal variables.

See Examples 3-10, 3-11, 3-12 and Exercises 3-11, 3-12, 3-13, 3-14, 3-15

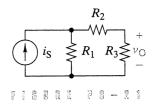

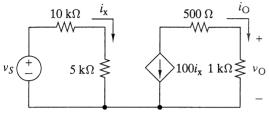

Find the proportionality constant  $K = v_0/i_s$  for the circuit in Figure P3–21.

3-22 Find the proportionality constant  $K = i_0/i_S$  for the circuit in Figure P3-22.

Find the proportionality constant  $K = v_0/i_S$  for the circuit in Figure P3-23.

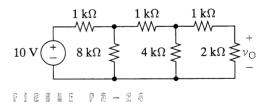

3-24 Use the unit output method to find  $v_0$  in the circuit in Figure P3-24.

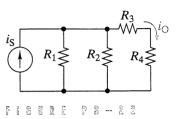

3-25 Use the unit output method to find  $i_0$  in the circuit in Figure P3-25.

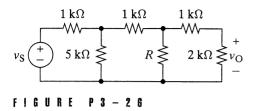

3-26 Use the unit output method to select R in the circuit in Figure P3-26 so that the proportionality constant  $K = v_O/v_S = 1/4$ .

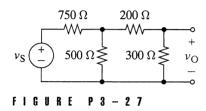

3-27 Find the proportionality constant  $K = v_0/v_s$  for the circuit in Figure P3-27.

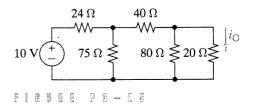

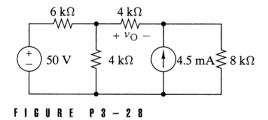

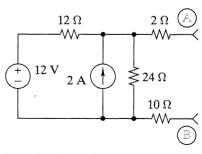

3-28 Use the superposition principle in the circuit of Figure P3-28 to find  $v_O$ .

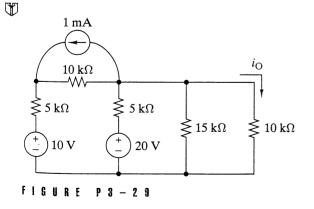

3-29 Use the superposition principle in the circuit of Figure P3-29 to find  $i_O$ .

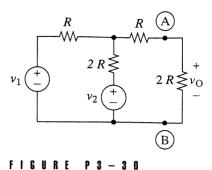

3-30 Use the superposition principle in the circuit of Figure P3-30 to find  $v_0$  in terms of  $v_1$ ,  $v_2$ , and R.

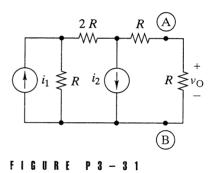

3-31 Use the superposition principle in the circuit of Figure P3-31 to find  $v_0$  in terms of  $i_1$ ,  $i_2$ , and R.

- 3-32 A linear circuit containing two sources drives a  $100-\Omega$  load resistor. Source number 1 delivers 250 mW to the load when source number 2 is off. Source number 2 delivers 4 W to the load when source number 1 is off. Find the power delivered to the load when both sources are on. *Hint*: The answer is not 4.25 W. Why?

- 3–33 A linear circuit is driven by an independent voltage source  $v_S = 10 \text{ V}$  and an independent current source  $i_S = 10 \text{ mA}$ . When the voltage source is on and the current source is off, the output voltage is  $v_O = 2 \text{ V}$ . When both sources are on, the output is  $v_O = 1 \text{ V}$ . Find the output when  $v_S = 5 \text{ V}$  and  $i_S = -10 \text{ mA}$ .

- 3-34 The following table lists test data of the output of a linear resistive circuit for different values of its three inputs. Find the input-output relationship for the circuit.

| $v_{\rm S1}({ m V})$ | $v_{ m S2}({ m V})$ | $v_{ m S3}({ m V})$ | $v_{\rm O}({\rm V})$ |

|----------------------|---------------------|---------------------|----------------------|

| 0                    | 4                   | -4                  | 0                    |

| 2                    | 0                   | 2                   | 1.5                  |

| 2                    | 4                   | 0                   | 2                    |

This problem involves designing a resistive circuit with two inputs  $v_{S1}$  and  $v_{S2}$  and a single output voltage  $v_O$ . Design the circuit so that  $v_O = K(v_{S1} + 3v_{S2})$  is delivered across a 500- $\Omega$  load. The value of K is not specified but should be greater than 1/20.

# ERO 3-3 Thévenin and Norton Equivalent Circuits (Sect. 3-4)

Given a circuit containing linear resistors and independent sources,

- (a) Find the Thévenin or Norton equivalent at a specified pair of terminals.

- (b) Use the Thévenin or Norton equivalent to find the signals delivered to linear or nonlinear loads.

See Examples 3-13, 3-14, 3-15, 3-16 and Exercises 3-16, 3-17, 3-18

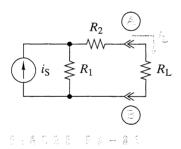

- (a) Find the Thévenin or Norton equivalent circuit seen by  $R_L$  in Figure P3–36.

- **(b)** Use the equivalent circuit found in (a) to find  $i_L$  in terms of  $i_S$ ,  $R_1$ ,  $R_2$ , and  $R_L$ .

- (c) Check your answer in (b) using current division.

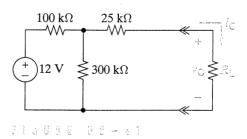

- (a) Find the Thévenin or Norton equivalent circuit seen by  $R_{\rm L}$  in Figure P3-37.

- (b) Use the equivalent circuit found in (a) to find load power when  $R_L = 50 \Omega$ ,  $100 \Omega$ , and  $500 \Omega$ .

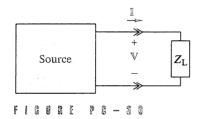

- (a) Find the Thévenin or Norton equivalent seen by  $R_1$  in Figure P3-38.

- (b) Use the equivalent circuit found in (a) to find load voltage when  $R_L = 10 \text{ k}\Omega$ , 25 k $\Omega$ , 50 k $\Omega$ , and  $100 \text{ k}\Omega$ .

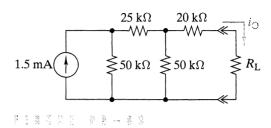

- (a) Find the Thévenin or Norton equivalent seen by  $R_1$  in Figure P3-39.

- (b) Use the equivalent circuit found in (a) to find  $i_0$  for  $R_L = 6 \text{ k}\Omega$ ,  $R_L = 12 \text{ k}\Omega$ , 24 k $\Omega$ , and 48 k $\Omega$ .

- (a) Find the Thévenin or Norton equivalent at terminals A and B in Figure P3-40.

- (b) Use the equivalent circuit to find interface power when a  $10-\Omega$  load is connected between terminals A and B.

- (c) Repeat (b) when a 5-V source is connected between terminals A and B with the plus terminal at terminal A.

医自复复音器 医有一方角

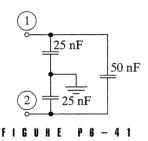

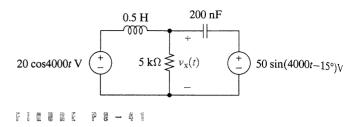

- 3-4 (a) Find the Thévenin or Norton equivalent seen to the left of terminals A and B in Figure P3-41. (*Hint*: Use source transformations and circuit reduction.)

- **(b)** Use the equivalent found in (a) to find the output  $v_0$  in terms of  $v_1$ ,  $v_2$ , and R.

FIGSHE F8-41

- 3-42 Figure P3-42 shows a source circuit with two accessible terminals. When i = 0 the output voltage is v = 10 V. When a 2.4-k $\Omega$  resistor is connected between the terminals the output drops to 6 V.

- (a) Find the Thévenin equivalent of the source.

- (b) Use the equivalent circuit to find the power the source would deliver to resistive loads of 500  $\Omega$ ,  $1 \text{ k}\Omega$ , and  $2 \text{ k}\Omega$ .

- 3–43 Figure P3–42 shows a source circuit with two accessible terminals. When a 300- $\Omega$  resistor is connected across the accessible terminals, the output current is i = 30 mA. When a 500- $\Omega$  resistor is connected, the output current is i = 20 mA. How much current would this source deliver to a 10-V source?

- 3-44 Figure P3-42 shows a source circuit with two accessible terminals. Some voltage and current measurements at the accessible terminals are

$$v(V) -10 -5 0 +5 +10 12 13 14$$

$i(mA) +5 +4 +3 +2 +1 0 -1 -2$

- (a) Plot the source  $i-\nu$  characteristic using these data.

- (b) Develop a Thévenin equivalent circuit valid on the range |v| < 10 V.

- (c) Use the equivalent circuit to predict the source ν<sub>OC</sub> and i<sub>SC</sub>.

- (d) Compare your results in (c) with the given measurements and explain any differences.

- The Thévenin equivalent parameters of a two-terminal source are  $v_T = 5 \text{ V}$  and  $R_T = 150 \Omega$ . Find the minimum allowable load resistance if the delivered load voltage must exceed 3.5 V.

- Use a sequence of source transformations to find the Thévenin equivalent at terminals A and B in Figure P3-46.

(a) Find the Thévenin or Norton equivalent seen by  $R_L$  in Figure P3–47.

- **(b)** Use the equivalent circuit to find the value of  $R_{\rm L}$  that produces  $v_{\rm O} = 6$  V.

- The current delivered to  $R_{\rm L}$  in Figure P3–47 is observed to be  $i_{\rm O}=36~\mu{\rm A}$ . Find the value of  $R_{\rm L}$ .

- A nonlinear resistor is connected across a two-terminal source whose Thévenin equivalent is  $v_T = 5 \text{ V}$  and  $R_T = 500 \Omega$ .

- (a) Plot the  $i-\nu$  characteristic of the source in the first quadrant  $(i \ge 0, \nu \ge 0)$ .

- (b) The i-v characteristic of the resistor is  $i=10^{-4}$  (v+2  $v^{3.3}$ ). Plot this characteristic on the source plot obtained in (a) and graphically determine the voltage across and current through the nonlinear resistor.

- 3–50 A nonlinear resistor is connected across a two-terminal source whose Thévenin equivalent is  $v_T = 10 \text{ V}$  and  $R_T = 200 \Omega$ .

- (a) Plot the  $i-\nu$  characteristic of the source in the first quadrant  $(i \ge 0, \nu \ge 0)$ .

- (b) The i-v characteristic of the resistor is  $v = 4000 i^2$ . Plot this characteristic on the source plot obtained in (a) and graphically determine the voltage across and current through the nonlinear resistor.

#### ERO 3-4 MAXIMUM SIGNAL TRANSFER (SECT. 3-5)

Given a circuit containing linear resistors and independent sources,

- (a) Find the maximum voltage, current, and power available at a specified pair of terminals.

- (b) Find the resistive loads required to obtain the maximum available signal levels.

See Example 3-17 and Exercise 3-19

- 3-51 (a) The load resistance in Figure P3-51 is adjusted until the maximum power is delivered. Find the power delivered and the value of  $R_L$ .

- **(b)** The load resistance is adjusted until maximum voltage is delivered. Find the voltage delivered and the value of  $R_{\rm L}$ .

- (c) The load resistance is adjusted until maximum current is delivered. Find the current delivered and the value of  $R_{\rm L}$ .

P 3 - 5 1

FIGURE

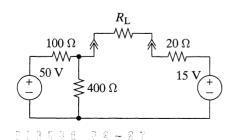

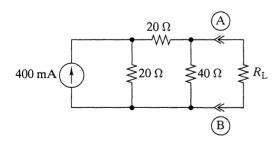

3-52 Find the maximum power available to the load resistance in Figure P3-52. What value of  $R_L$  will extract maximum power?

3-53 Find the maximum power available to the load resistance in Figure P3-53. What value of R<sub>L</sub> will extract maximum power?

3-54 The resistance R in Figure P3-54 is adjusted until maximum power is delivered across the interface to the load consisting of R and the 6-k $\Omega$  resistor in parallel. Find the voltage and power delivered to the load and the value of R.

3-55 When a 2-k $\Omega$  resistor is connected across a two-terminal source, a current of 0.75 mA is delivered to the load. When a second 2-k $\Omega$  resistor is connected in parallel with the first, a total current of 1 mA is delivered. Find the maximum power available from the source and specify the load resistance required to extract maximum power from the source.

- 3-56 (a) The potentiometer in Figure P3-56 is adjusted until maximum power is delivered to the 2-k $\Omega$  load. Find the wiper position x. Caution: The load is fixed.

- (b) The potentiometer in Figure P3-56 is adjusted until maximum voltage is delivered to the  $2-k\Omega$  load. Find the wiper position x.

3-57 Find the value of  $R_L$  in Figure P3-57 such that  $i_L = 3 \text{ mA}$ .

- 3-58 Find the value of  $R_L$  in Figure P3-57 such that  $v_L = 5 \text{ V}$

- 3-59 A 15-V source with 100  $\Omega$  internal resistance is connected in series with a resistor  $R_{\rm S}$ . Select the value of  $R_{\rm S}$  so that outputs of the series combination are bounded by i < 50 mA and p < 200 mW for any load resistance.

- 3-60 A practical source delivers 50 mA to a 300- $\Omega$  load. The source delivers 12 V to a 120- $\Omega$  load. Find the maximum power available from the source.

### ERO 3-5 INTERFACE CIRCUIT DESIGN (SECT. 3-6)

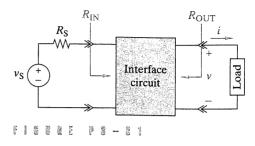

Given the signal transfer objectives at a source-load interface, adjust the circuit parameters or design one or more two-port interface circuits to achieve the specified objectives within stated constraints. See Examples 3–18, 3–19, 3–20, 3–21, 3–22 and Exercises 3–20, 3–21

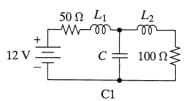

3-61 Figure P3-61 shows a two-port interface circuit connecting source and load circuits. In this problem  $v_S = 10 \text{ V}$ ,  $R_S = 50 \Omega$ , and the load is a 50- $\Omega$  resistor. To

avoid damaging the source, its output current must be less than 100 mA. Design a resistive interface circuit so that the voltage delivered to the load is 4 V and the source current is less than 100 mA.

3-62 Figure P3-61 shows a two-port interface circuit connecting source and load circuits. In this problem  $v_S = 15 \text{ V}$ ,  $R_S = 1 \text{ k}\Omega$ , and the load is a diode whose i- $\nu$  characteristic is

$$i = 10^{-15}(e^{40v} - 1)$$

Design an interface circuit that dissipates less than 50 mW and produces an interface voltage of v = 0.7 V.

- Figure P3-61 shows a two-port interface circuit connecting source and load circuits. In this problem  $v_S$  = 15 V,  $R_S$  = 100  $\Omega$ , and the load is a 2-k $\Omega$  resistor. Design a resistive interface circuit so that the voltage delivered to the load is 10 V ±10% using one or more of the following standard resistors: 68  $\Omega$ , 100  $\Omega$ , 220  $\Omega$ , 330  $\Omega$ , 470  $\Omega$ , and 680  $\Omega$ . The resistors all have a tolerance of ±5%, which you must account for in your design.

- 3-64 In Figure P3-61 the load is a 500- $\Omega$  resistor and  $R_S = 75 \Omega$ . Design an interface circuit so that the input resistance of the two-port is 75  $\Omega$  ±10% and the output resistance seen by the load is 500  $\Omega$  ±10%.

- Use the resistor array in Figure P3-65 to design a two-port resistance circuit whose voltage gain  $K = v_0/v_{IN}$  is at least 0.6 and whose input resistance is close to  $100 \Omega$ .

- 3-66 Pigure P3-61 shows a two-port interface circuit connecting source and load circuits. In this problem  $v_S = 12 \text{ V}$ ,  $R_S = 300 \Omega$ , and the load is a 50- $\Omega$  resistor. Design an interface circuit so that v < 2 V and i > 40 mA.

- 3-67 Pigure P3-61 shows a two-port interface circuit connecting source and load circuits. In this problem  $v_{\rm S}=10~{\rm V},\,R_{\rm S}=50~\Omega,$  and the load is a 50- $\Omega$  resistor. Design an interface so that 350 mW is delivered to the load.

- 3-68 Figure P3-61 shows a two-port interface circuit connecting a source and load. In this problem the source with  $v_S = 5$  V and  $R_S = 5$   $\Omega$  is to be used in production testing of two-terminal semiconductor devices. The devices are to be connected as the load in Figure P3-61 and have highly nonlinear and variable i-v characteristics. The normal operating range for acceptable devices is  $\{i > 10 \text{ mA} \text{ or } v > 0.7 \text{ V}\}$  and  $\{p < 10 \text{ mW}\}$ . Design an interface circuit so that the operating point always lies within the specified normal range regardless of the test article's i-v characteristic.

- 3-69 Figure P3-69 shows an interface circuit connecting a source circuit and a load. Design an interface circuit so that  $\nu < 4$  V regardless of the load resistance.

3-70 Design the interface circuit in Figure P3-69 so that the power delivered to the load never exceeds 1 mW regardless of the load resistance.

## INTEGRATING PROBLEMS

#### 3-71 🐞 COMPARISON OF ANALYSIS METHODS

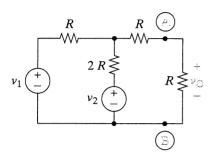

The circuit in Figure P3–71 is called an *R-2R* ladder for obvious reasons. The additive property of linear circuits states that the output of the form

$$v_{\rm O} = k_1 v_1 + k_2 v_2 + k_3 v_3$$

We could use superposition to find the gains  $k_1$ ,  $k_2$ , and  $k_3$ . But applying the input sources one at a time may not be the best way to find these gains. The purpose of this problem is to compare two other methods.

(a) Write node-voltage equations for the circuit in Figure P3-71 using node B as the reference node. Solve these equations to show that  $v_O = v_1/8 + v_2/4 + v_3/2$ .

- **(b)** We can also use circuit reduction techniques since the circuit is a ladder. Use successive source transformations and series/parallel equivalence to reduce the circuit between nodes A and B to a single equivalent voltage source connected in series with an equivalent resistor. Use this equivalent circuit to show that  $v_{\rm O} = v_1/8 + v_2/4 + v_3/2$ .

- (c) Which method do you think is easier and why?

FIGURE P2-71

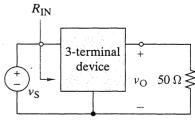

#### 3-72 M THREE-TERMINAL DEVICE MODELING

Figure P3-72 shows a three-terminal device with a voltage source  $v_s$  connected at the input and a 50- $\Omega$  load resistor connected at the output. The purpose of the problem is to develop an input-output relationship for the device using the following experimental data.

$$v_{\rm S}({\rm V})$$

-12 -9 -6 -3 0 +3 +6 +9 +12  $v_{\rm O}({\rm V})$  3 2.5 2 1 0 -1 -2 -2 -2

The device input resistance is  $R_{\rm IN} = 1~{\rm k}\Omega$  when the 50- $\Omega$  load is connected at the output.

- (a) Plot  $v_0$  versus  $v_s$  and state whether the graph is linear or nonlinear.

- **(b)** Devise a linear model of the form  $v_O = Kv_S$  that approximates the data for  $|v_S| < 6 \text{ V}$ .

- (c) Use your model from part (b) to predict the circuit output for  $v_S = \pm 10 \text{ V}$  and explain why the predictions do not agree with the experimental results.

- (d) For  $v_S = 1$  V use your model from part (c) to find the circuit power gain =  $P_O/P_{IN}$ .

- (e) In view of the result in (d), is the device active or passive?

FIGURE P3-72

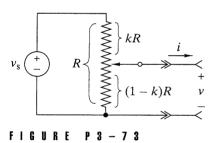

## 3-73 A ADJUSTABLE THÉVENIN EQUIVALENT

Figure P3–73 shows an ideal voltage source in parallel with an adjustable potentiometer. This problem concerns the effect of adjusting the potentiometer on the interface Thévenin equivalent circuit and the signals available at the interface.

- (a) Find the parameters  $v_T$  and  $R_T$  of the Thévenin equivalent circuit at the interface in terms of circuit parameters k,  $v_S$ , and R.

- (b) Find the value of  $R_T$  for k = 0, k = 0.5, and k = 1. Explain your results physically in terms of the position of the movable arm of the potentiometer.

- (c) What is the power available at the interface for k = 0, k = 0.5, and k = 1? Justify your answers physically in terms of the position of the movable arm of the potentiometer.

- (d) A load resistor  $R_L = R/4$  is connected across the interface. Where should the potentiometer be positioned (k = ?) to transfer the maximum power to this load?

- (e) A load resistor  $R_L = R/4$  is connected across the interface. Where should the potentiometer be positioned (k = ?) to deliver an interface voltage  $v = v_S/4$  to this load?

#### 3-74 D BATTERY DESIGN

A satellite requires a battery with an open-circuit voltage  $v_{\rm OC}=36~{\rm V}$  and a Thévenin resistance  $R_{\rm T}\leq 10~\Omega$ . The battery is to be constructed using series and parallel combinations of one of two types of cells. The first type has  $v_{\rm OC}=9~{\rm V}$ ,  $R_{\rm T}=4~\Omega$ , and a weight of 40 grams. The second type has  $v_{\rm OC}=4~{\rm V}$ ,  $R_{\rm T}=0.5~\Omega$ , and a weight of 15 grams. Design a minimum weight battery to meet the open-circuit voltage and Thévenin resistance requirements.

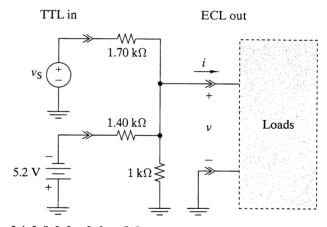

#### 3-75 ♠ TTL TO ECL CONVERTER

It is claimed that the resistive circuit in Figure P3–75 converts transistor-transistor logic (TTL) input signals into output signals compatible with emitter coupled logic (ECL). Specifically, the claim is that for any output current in the range -0.025 mA  $\leq i \leq 0.025$  mA, the circuit converts any input in the TTL low range  $(0 \leq v_s \leq 0.4 \text{ V})$  to an output in the ECL low range  $(-1.7 \text{ V} \leq v \leq -1.5 \text{ V})$ , and converts any input in the TTL high range  $(3.0 \leq v_s \leq 3.8 \text{ V})$  to an output in the ECL high range  $(-0.9 \text{ V} \leq v \leq -0.6 \text{ V})$ . The purpose of this problem is to verify this claim.

(a) The output voltage can be written in the form

$$v = k_1 v_{\rm S} + k_2 i$$

Write a KCL equation at the output with the current i as an unknown and solve for the constants  $k_1$  and  $k_2$ .

(b) Use the relationship found in (a) to verify that the output voltage falls in one of the allowed ECL ranges for every allowed combination of TTL inputs and load currents.

FIGURE P3-75

### SUMMARY

- The output of a dependent source is controlled by a signal in a different part of the circuit. Linear dependent sources are circuit elements used to model active devices and are represented in this text by a diamond-shaped source symbol. Each type of controlled source is characterized by a single-gain parameter μ, β, r, or g.

- The Thévenin resistance of a circuit containing dependent sources can be found using the open-circuit voltage and the short-circuit current, or by directly solving for the interface i-v characteristic. The active Thévenin resistance may be significantly different from the passive lookback resistance.

- The large-signal model describes the BJT in terms of cutoff, active, and saturation modes. Each mode has a unique set of *i*- $\nu$  characteristics. The operating mode must be determined to correctly analyze a transistor circuit. The operating mode can be determined by calculating the circuit responses assuming that the device is in the active mode and then comparing the calculated responses with known bounds.

- The OP AMP is an active device with at least five terminals: the inverting input, the noninverting input, the output, and two power supply terminals. The power supply terminals are not usually shown in circuit diagrams. The integrated circuit OP AMP is a differential amplifier with a very high voltage gain.

- The OP AMP can operate in a linear mode when there is a feedback path from the output to the inverting input. To remain in the linear mode, the output voltage is limited to the range  $-V_{\rm CC} \le v_{\rm O} \le +V_{\rm CC}$ , where  $\pm V_{\rm CC}$  are the supply voltages.

- $^{\circ}$  The i-v characteristics of the ideal model of an OP AMP are  $i_{\rm P}$  =  $i_{\rm N}$  = 0 and  $v_{\rm P}$  =  $v_{\rm N}$ . The ideal OP AMP has an infinite voltage gain, an infinite input resistance, and zero output resistance. The ideal model is a good approximation to real devices as long as the circuit gain is much smaller than the OP AMP gain.

- Four basic signal-processing functions performed by OP AMP circuits are the inverting amplifier, noninverting amplifier, inverting summer, and differential amplifier. These arithmetic operations can also be represented in block diagram form.

- OP AMP circuits can be connected in cascade to obtain more complicated signal-processing functions. The analysis and design of the individual stages in the cascade can be treated separately, provided the input resistance of the following stage is kept sufficiently high.

- OP AMP circuits are easily treated using node analysis. A node voltage is identified at each OP AMP output, but a node equation is not written at these nodes. Node equations are then written at the remaining nodes, and the ideal OP AMP input voltage constraint  $(v_N = v_P)$  is used to reduce the number of unknowns.

- The comparator is a nonlinear signal-processing device obtained by operating an OP AMP device without feedback. The comparator has two analog inputs and a two-state digital output.

## PROBLEMS

# ERO 4-1 LINEAR ACTIVE CIRCUITS (SECTS. 4-1, 4-2)

Given a circuit containing linear resistors, dependent sources, and independent sources, find selected output signal variables, input-output relationships, or input-output resistances.

See Examples 4–2, 4–3, 4–4, 4–5, 4–6, 4–7, 4–8 and Exercises 4–1, 4–2, 4–3, 4–5, 4–6

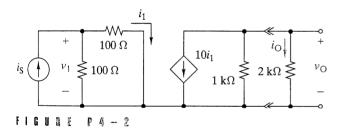

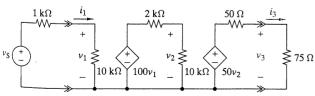

4-1 Find the voltage gain  $v_0/v_s$  and current gain  $i_0/i_x$  in Figure P4-1.

FIGURE P4-1

4–2 Find the voltage gain  $v_O/v_1$  and the current gain  $i_O/i_S$  in Figure P4–2. For  $i_S = 2$  mA, find the power supplied by the input source  $i_S$  and the power delivered to the 2-k $\Omega$  load resistor.

4-3 The circuit in Figure P4-3 is a dependent-source model of a two-stage amplifier.

Find the output voltage  $v_3$  and the current gain  $i_3/i_1$  when  $v_5 = 1$  mV.

FIGURE P4-3

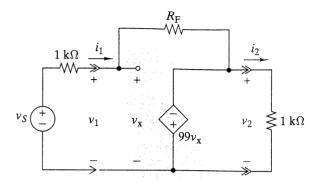

- 4–4 The circuit in Figure P4–4 is an ideal voltage amplifier with negative feedback provided via the resistor  $R_{\rm E}$ .

- (a) Find the output voltage  $v_2$  and the current gain  $i_2/i_1$  when  $v_S = 10$  mV and  $R_F = 10$  k $\Omega$ .

- **(b)** Find the input resistance  $R_{IN} = v_1/i_1$ .

FIGURE P4-4

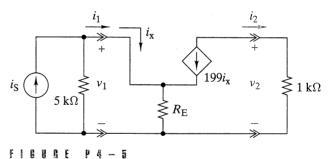

- 4–5 The circuit in Figure P4–5 is an ideal current amplifier with negative feedback via the resistor  $R_{\rm E}$ .

- (a) Find the output current  $i_2$  and the voltage gain  $v_2/v_1$  when  $i_S = 25 \mu A$  and  $R_E = 450 \Omega$ .

- **(b)** Find the input resistance  $R_{IN} = v_1/i_1$ .

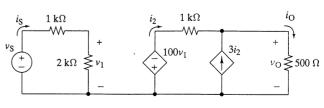

4–6 Find the voltage gain  $v_{\rm O}/v_{\rm S}$  and the current gain  $i_{\rm O}/i_{\rm S}$  in Figure P4–6.

FIGURE P4-8

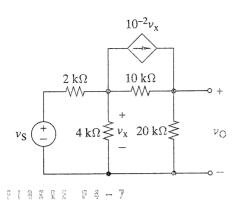

4-7 Find the voltage gain  $v_0/v_s$  in Figure P4-7.

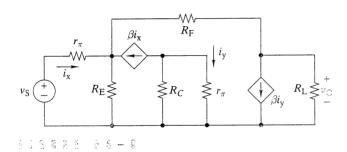

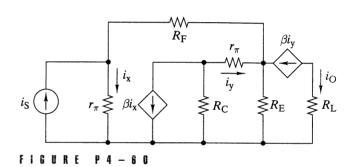

The circuit in Figure P4–8 is a model of a feedback amplifier using two identical transistors. Formulate either node-voltage or mesh-current equations for this circuit. Use these equations to solve for the input-out-put relationship  $v_{\rm O}=Kv_{\rm S}$  using  $r_{\pi}=1$  k $\Omega$ ,  $R_{\rm E}=200$   $\Omega$ ,  $R_{\rm C}=10$  k $\Omega$ ,  $R_{\rm L}=5$  k $\Omega$ ,  $R_{\rm F}=5$  k $\Omega$ , and  $\beta=100$ .

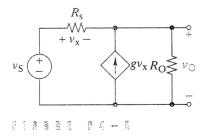

Find an expression for the voltage gain  $v_0/v_s$  in Figure P4–9.

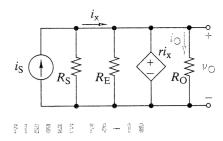

4-10 Find an expression for the current gain  $i_0/i_S$  in Figure P4-10.

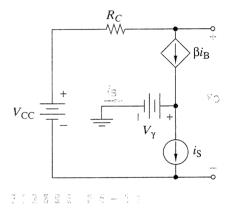

The circuit in Figure P4-11 is a model of a bipolar junction transistor operating in the active mode. The input signal is the current source  $i_{\rm S}$ , and the voltage source  $V_{\rm CC}$  supplies power. Find expressions for the base current  $i_{\rm B}$  and the output voltage  $v_{\rm O}$  in terms of  $V_{\rm CC}$  and  $i_{\rm S}$ .

Find the Thévenin equivalent circuit seen by the resistor  $R_L$  in Figure P4-12.

### ERO 4-2 TRANSISTOR CIRCUITS (SECT. 4-3)

Given a linear resistive circuit with one transistor,

- (a) Find the transistor operating mode and circuit responses.

- (b) Select circuit parameters to obtain a specified operating mode.

See Examples 4-9, 4-10, 4-11 and Exercises 4-7, 4-8

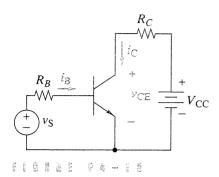

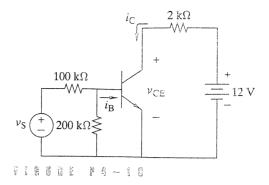

4–13 In Figure P4–13 the circuit parameters are  $R_{\rm B} = 50 \ {\rm k}\Omega$ ,  $R_{\rm C} = 2 \ {\rm k}\Omega$ ,  $\beta = 100$ ,  $V_{\gamma} = 0.7 \ {\rm V}$ , and  $V_{\rm CC} = 10 \ {\rm V}$ . Find  $i_{\rm C}$  and  $v_{\rm CE}$  for  $v_{\rm S} = 2 \ {\rm V}$ . Repeat for  $v_{\rm S} = 5 \ {\rm V}$ .

- 4-14 In Figure P4-13 the circuit parameters are  $R_{\rm B} = 50~{\rm k}\Omega,~R_{\rm C} = 5~{\rm k}\Omega,~\beta = 50,~V_{\gamma} = 0.6~{\rm V},~{\rm and}~V_{\rm CC} = 15~{\rm V}.$  Find the range of  $v_{\rm S}$  for which the transistor operates in the active mode.

- 4–15 In Figure P4–13 the circuit parameters are  $R_{\rm B}=20~{\rm k}\Omega,\,R_{\rm C}=470~\Omega,\,\beta=150,\,V_{\gamma}=0.7~{\rm V},\,{\rm and}\,V_{\rm CC}=15~{\rm V}.$  Find the range of  $v_{\rm S}$  for which the transistor operates in the saturation mode.

- 4-16 In Figure P4-13 the circuit parameters are  $R_{\rm C} = 1~{\rm k}\Omega$ ,  $\beta = 75$ ,  $V_{\gamma} = 0.7~{\rm V}$ ,  $V_{\rm CC} = 20~{\rm V}$ , and  $v_{\rm S} = 2.5~{\rm V}$ . Select a value of  $R_{\rm B}$  so that the transistor is in the active mode with  $v_{\rm CE} = V_{\rm CC}/2$ .

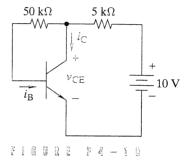

- 4-17 In Figure P4-17 the transistor parameters are  $\beta = 150$  and  $V_{\gamma} = 0.7$  V. Find  $i_{\rm C}$  and  $v_{\rm CE}$  for  $v_{\rm S} = 0.5$  V. Repeat for  $v_{\rm S} = 1$  V.

4–18 In Figure P4–18 the transistor parameters are  $\beta=80$  and  $V_{\gamma}=0.7$  V. Find  $i_{\rm C}$  and  $v_{\rm CE}$  for  $v_{\rm S}=1$  V. Repeat for  $v_{\rm S}=4$  V.

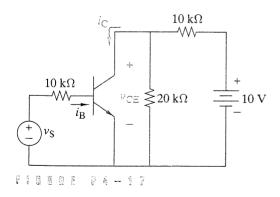

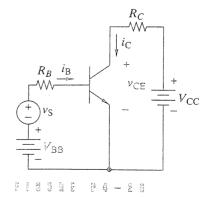

In Figure P4–19 the transistor parameters are  $\beta = 100$  and  $V_{\gamma} = 0.7$  V. Find  $i_{\rm C}$  and  $v_{\rm CE}$ .

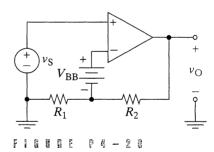

- The input in Figure P4–20 is a series connection of a dc source  $V_{\rm BB}$  and a signal source  $v_{\rm S}$ . The circuit parameters are  $R_{\rm B}=500~{\rm k}\Omega$ ,  $R_{\rm C}=5~{\rm k}\Omega$ ,  $\beta=100$ ,  $V_{\gamma}=0.7~{\rm V}$ , and  $V_{\rm CC}=15~{\rm V}$ .

- (a) With  $v_S = 0$ , select the value of  $V_{BB}$  so that the transistor is in the active mode with  $v_{CE} = V_{CC}/2$ .

- (b) Using the value of V<sub>BB</sub> found in (a), find the range of values of the signal voltage ν<sub>S</sub> for which the transistor remains in the active mode.

- (c) Plot the transfer characteristic  $v_{CE}$  versus  $v_{S}$  as the signal voltage sweeps across the range from -10 V to +10 V.

# ERO 4-3 OP AMP CIRCUIT ANALYSIS (SECTS. 4-4, 4-5)

Given a circuit consisting of linear resistors, OP AMPs, and independent sources, find selected output signals or inputoutput relationships in equation or block diagram form. See Examples 4–13, 4–14, 4–16, 4–17, 4–18, 4–19 and Exercises 4–10, 4–11, 4–12, 4–13, 4–15, 4–16

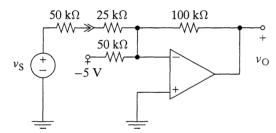

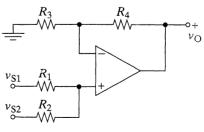

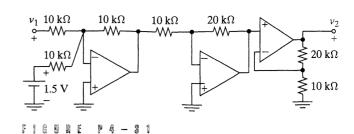

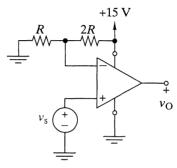

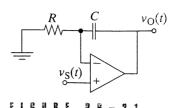

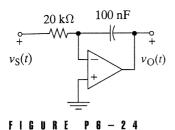

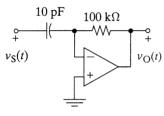

**4–21** Find  $v_0$  in terms of  $v_s$  in Figure P4–21.

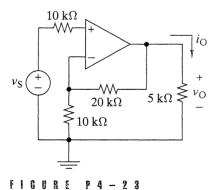

4–22 Find  $v_0$  in terms of  $v_s$  in Figure P4–22.

P4-21

FIGURE

FIGURE P4-22

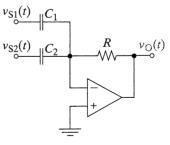

- **4–23** (a) Find  $v_0$  in terms  $v_S$  in Figure P4–23.

- **(b)** Find  $i_0$  for  $v_S = 1.5$  V.

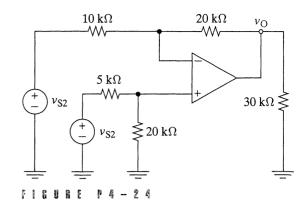

**4–24** (a) Find  $v_0$  in terms of  $v_{S1}$  and  $v_{S2}$  in Figure P4–24.

(b) For  $V_{CC} = \pm 15 \text{ V}$  and  $v_{S2} = 10 \text{ V}$ , find the allowable range of  $v_{S1}$  for linear operation.

4-25 The input-output relationship for a three-input inverting summer is

$$v_{\rm O} = -[v_1 + 3v_2 + 5v_3]$$

The resistance of the feedback resistor is 75 k $\Omega$ , and the supply voltages are  $V_{\rm CC}$  = ±15 V.

- (a) Find the values of the input resistors  $R_1$ ,  $R_2$ , and  $R_2$ .

- **(b)** For  $v_2 = 0.5$  V and  $v_3 = -1$  V, find the allowable range of  $v_1$  for linear operation.

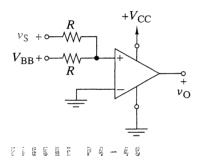

- **4–26** (a) Find  $v_0$  in terms  $v_S$  and  $V_{BB}$  in Figure P4–26.

- **(b)** For  $V_{CC} = \pm 15$  V,  $V_{BB} = 5$  V, and  $R_1 = R_2$ , sketch the  $v_O$  versus  $v_S$  for  $v_S$  on the range from -15 V to +15 V.

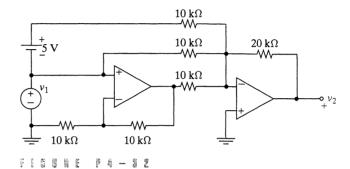

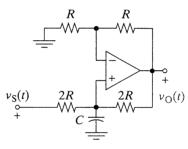

4–27 Find  $v_0$  in terms of  $v_{S1}$  and  $v_{S2}$  in Figure P4–27

FIGURE P4-27

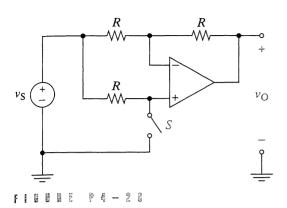

4-28 It is claimed that  $v_O = v_S$  when the switch is closed in Figure P4-28 and that  $v_O = -v_S$  when the switch is open. Prove or disprove this claim.

4-29 What range of gain is available from the circuit in Figure P4-29?

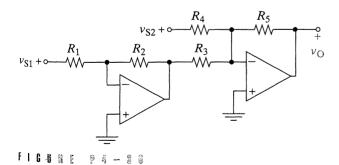

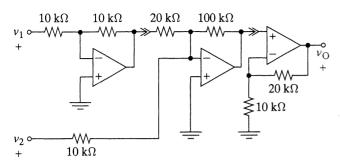

4–30 Find  $v_0$  in terms of  $v_{S1}$  and  $v_{S2}$  in Figure P4–30.

4-31 Find the output  $v_2$  in terms of the input  $v_1$  in Figure P4-31.

4-32 Find the output  $v_2$  in terms of the input  $v_1$  in Figure P4-32.

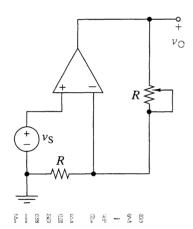

4-33 Find the output  $v_0$  in terms of the input  $v_s$  in Figure P4-33.

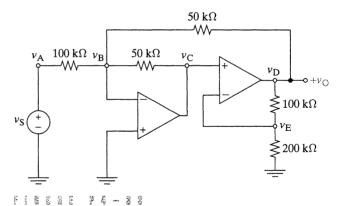

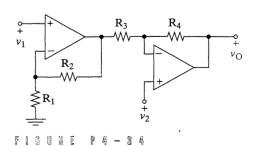

4-34 Find the output  $v_0$  in terms of  $v_1$  and  $v_2$  in Figure P4-34.

4–35 Find the output  $v_0$  in terms of  $v_1$  and  $v_2$  in Figure P4–35.

FIGURE P4-35

#### ERO 4-4 OP AMP CIRCUIT DESIGN (SECT. 4-6)

Given an input-output relationship, use resistors and OP AMPs to design one or more circuits that implement the relationship within stated constraints.

See Examples 4-15, 4-20, 4-21, 4-22, 4-23 and Exercise 4-16

4-37 Design circuits using resistors and OP AMPs to implement each of the following input-output relationships:

(a)

$$v_0 = 3v_1 - 2v_2$$

**(b)**

$$v_0 = 2v_1 + v_2$$

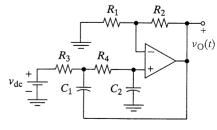

Design a signal conditioning circuit for the temperature transducer whose characteristics are shown in Figure P4–38. The conditioning circuit must convert the transducer output for temperatures between -300 °C and -100 °C to a range of 0 to 5 V. The voltage gain for all stages must be less than 1000.

4-39 The resistance of a pressure transducer varies from 5 k $\Omega$  to 15 k $\Omega$  when the pressure varies over its specified operating range. Design a signal conditioning circuit to convert the sensor resistance variation to a voltage signal on the range from 0 to 5 V.

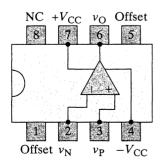

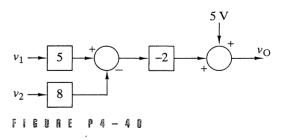

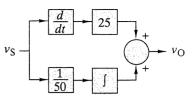

4-40 Design an OP AMP circuit that implements the block diagram in Figure P4-40 using only standard resistance values for ±5% tolerance (see Appendix A Table A-1).

4–41 Design an OP AMP circuit summer that implements a 3-bit D/A converter defined by

$$v_{\rm O} = K(4v_1 + 2v_2 + v_3)$$

The digital inputs  $(v_1, v_2, v_3)$  are either 0 V or 5 V. The analog output  $(v_0)$  must fall in the range of 0 V to 10 V for all possible inputs.

- An instrumentation system combines the outputs of three transducers into a single output using gains of -20, 3, and 18. Each transducer has a Thévenin resistance of 600  $\Omega$  and a Thévenin voltage in the range +120 mV. Design an OP AMP circuit to meet these requirements.

- A requirement exists for an amplifier with a gain of -12,000 and an input resistance of at least 300 k $\Omega$ . Design an OP AMP circuit that meets the requirements using general-purpose OP AMPs with voltage gains of  $A = 2 \times 10^5$ , input resistances of  $R_1 = 4 \times 10^8 \Omega$ , and output resistances  $R_{\rm O} = 20 \ \Omega$ .

- The potentiometer in Figure P4-44 is used as a position sensor. The range of mechanical input moves the wiper between the bottom and the top of the potentiometer. An interface circuit is required to convert the  $v_{\rm p}$  range (-15 to +15 V) to a  $v_{\rm O}$  range (0 to 5 V) suitable for input to the analog-to-digital converter. Design a suitable interface circuit.

FIGUR

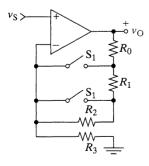

D Select the resistances in Figure P4-45 to produce the following gains

| , gams. |        |    |

|---------|--------|----|

| $S_1$   | $S_1$  | K  |

| open    | open   | 10 |

| open    | closed | 5  |

| closed  | x      | 2  |

FIGURE P4-45

#### ERO 4-5 THE COMPARATOR (SECT. 4-7)

Given a circuit with one or more comparators, find the circuit input-output relationship. See Examples 4-25, 4-26

- 4-46 The circuit in Figure P4-46 has  $V_{OH} = 15 \text{ V}$  and  $V_{\rm OL} = 0 \text{ V}.$

- (a) Determine the input voltage ranges for which  $v_0$  =  $V_{\rm OH}$  and  $v_{\rm O} = V_{\rm OL}$ .

- **(b)** Sketch the circuit transfer characteristics for  $v_s$  on the range from -15 V to +15 V.

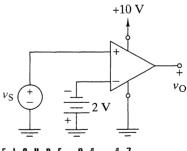

- 4-47 The circuit in Figure P4-47 has  $V_{OH} = 10 \text{ V}$  and  $V_{\rm OL} = 0 \text{ V}.$

- (a) Determine the input voltage ranges for which  $v_0 =$  $V_{\rm OH}$  and  $v_{\rm O} = V_{\rm OL}$ .

- **(b)** Sketch the circuit transfer characteristics for  $v_S$  on the range from -15 V to +15 V.

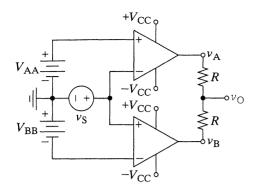

4-48 The circuit in Figure P4-48 is called a window detector. In this circuit the OP AMP saturation levels are  $\pm V_{\rm CC}$ . For  $V_{\rm CC}$  = 15 V,  $V_{\rm AA}$  = 10 V, and  $V_{\rm BB}$  = 5 V, show that output is determined by the following state-

If

$$(-V_{BB} < v_S < V_{AA})$$

then  $v_O = 15$  V else  $v_O = 0$ .

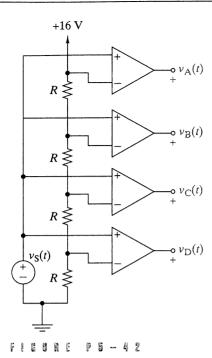

FIGURE P4-42

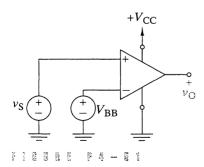

The circuit in Figure P4–49 has  $V_{\rm CC}$  = 15 V and  $V_{\rm BB}$  = -5 V.

- (a) Determine the input voltage ranges for which  $v_{\rm O} = V_{\rm OH}$  and  $v_{\rm O} = V_{\rm OL}$ .

- (b) Sketch the circuit transfer characteristics for  $v_s$  on the range from -10 V to +10 V.

4-50 Repeat Problem 4-49 with  $V_{\rm BB} = 5$  V. 4-51 The circuit in Figure P4-51 has  $V_{\rm CC} = 15$  V and  $V_{\rm BB} = 5$

5 V. Sketch the output voltage  $v_0$  on the range  $0 \le t$  $\le 2 \text{ s for } v_s = 10 \sin(2\pi t) \text{ V}.$

4-52 Repeat Problem 4-51 with  $V_{BB}(t) = 10t \text{ V}$ .

# INTEGRATING PROBLEMS

#### 4-53 & Bridged-T Inverting Amplifier

Using the basic inverting OP AMP configuration to obtain a large voltage gain requires a small input resistor, a large feedback resistor, or both. Small input resistors load the input source, and large  $(R>1~{\rm M}\Omega)$  feedback resistors have more noise and exhibit greater life-cycle variations. The circuit in Figure P4–53 circumvents these problems by using a bridged-T circuit in the feedback path. Note that  $R_3$  occurs twice in this diagram.

(a) Show that the gain of the circuit in Figure P4-53 can be written as  $K = -R_{\rm FDBK}/R_1$ , where  $R_{\rm FDBK}$  is the effective feedback resistance defined as:

$$R_{\text{FDBK}} = R_3 \left( 2 + \frac{R_3}{R_2} \right)$$

- (b) Design a basic inverting amplifier to achieve K = -400 and  $R_{\rm IN} \ge 20 \text{ k}\Omega$ .

- (c) Design a bridged-T inverting amplifier to achieve K = -400 and  $R_{\rm IN} \ge 20 \ \rm k\Omega$ .

- (d) Evaluate the two designs by comparing their element counts, element spreads (ratio of largest over smallest resistance), and total resistances (sum of all resistances).

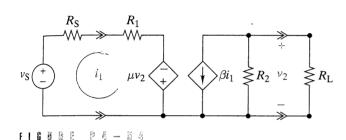

#### 4-54 🦀 HYBRID CIRCUIT ANALYSIS

The two-port interface circuit in Figure P4–54 is a small-signal model of a bipolar junction transistor using what are called hybrid parameters. The analysis of this circuit illustrates that it can be useful to use a mixture

(or hybrid) of mesh-current and node-voltage equations.

- (a) Using the symbolic notation in the figure, write a mesh-current equation for the input circuit and a node-voltage equation for the output circuit.

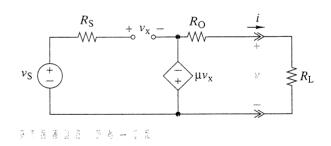

- (b) Using  $R_S = 2 \text{ k}\Omega$ ,  $R_1 = 5 \text{ k}\Omega$ ,  $R_2 = 50 \text{ k}\Omega$ ,  $R_L = 150 \text{ k}\Omega$ ,  $\mu = 10^{-3}$ , and  $\beta = 50$ , solve the equations from (a) for the input current  $i_1$  and the output voltage  $v_2$  in terms of the input  $v_S$ .

- (c) Using the results from (b), solve for the input resistance and the voltage gain of the circuit.

- (d) Calculate the power gain defined as the ratio of the power delivered to  $R_{\rm L}$  divided by the power supplied by  $v_{\rm S}$ .

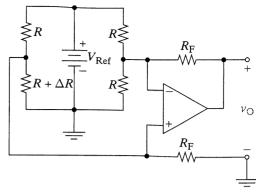

## 4-55 & WHEATSTONE BRIDGE AMPLIFIER

The circuit in Figure P4–55 shows a Wheatstone bridge consisting of three equal resistors and a fourth resistor that is a transducer whose resistance is  $R + \Delta R$ , where  $\Delta R << R$ . The bridge is excited by a constant reference voltage source  $V_{\rm REF}$  and is connected to the inputs of an OP AMP. For  $\Delta R << R$  the OP AMP output voltage can be expressed in the form

$$v_O = K \left[ \frac{\Delta R}{R} \right] V_{\rm REF}$$

- (a) Verify that this expression is correct and express K in terms of circuit parameters.

- (b) For  $V_{\rm REF} = 15$  V, R = 100  $\Omega$  and  $\Delta R/R$  in the range  $\pm 0.04\%$ , select value  $R_{\rm F}$  so that the output voltage  $v_{\rm O}$  falls in the range  $\pm 3$  V.

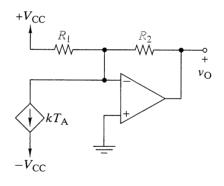

#### 4-56 TEMPERATURE SENSOR DESIGN

Figure P4–56 shows a circuit with a semiconductor temperature sensor modeled as a temperature-controlled current source. The device senses absolute temperature  $T_{\rm A}$  (°K) and delivers a current  $kT_{\rm A}$ , where  $k=1~\mu{\rm A}/{\rm °K}$ . The purpose of the OP AMP circuit is to make the output voltage proportional to °C. For  $V_{\rm CC}=10~{\rm V}$ , select values for  $R_1$  and  $R_2$  so that output voltage sensitivity is  $100~{\rm mV}/{\rm °C}$ .

FIGURE 74-56

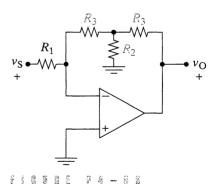

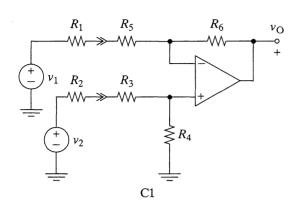

#### 4-57 & B SUBTRACTOR CIRCUITS

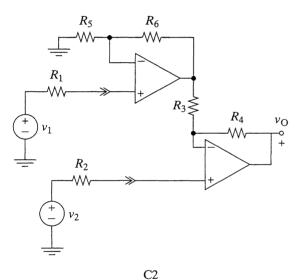

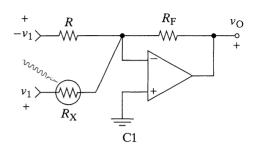

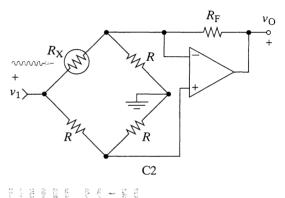

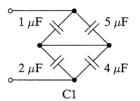

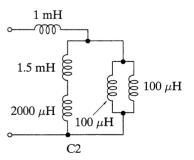

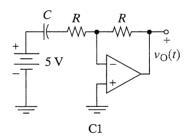

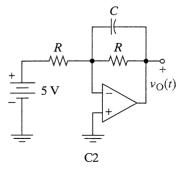

- The input-output relationship for both circuits in Figure P4-57 are of the form  $v_0 = K_2v_2 + K_1v_1$ .

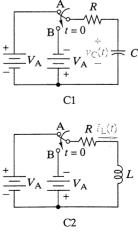

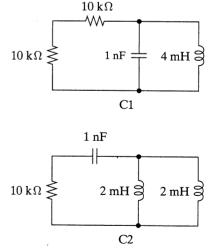

- (a)  $\mathbb{R}$  For circuits C1 and C2, determine the constants  $K_1$  and  $K_2$  in terms of circuit parameters.