# PHASE-LOCKED LOOPS1

Phase-locked loops (PLLs for short) go back to 1932 when deBellescizi used a tube-based phase-locked loop to synchronously demodulate radio signals. Today, PLLs are used in devices ranging from coherent analog receivers and carrier tracking filters to horizontal and vertical synchronization circuits in television sets. For those that are more digitally inclined, PLLs are also used for frequency synthesis, bit synchronization in digital data transmission, coherent FSK demodulation, and the like.

# SYSTEM BEHAVIOR

We will attempt to describe the system performance in terms of observable and measurable, i.e. engineering, quantities. There are two distinct modes of phase-locked loop behavior – ACQUISITION and TRACKING. In the ACQUISITION mode, the PLL is trying to lock onto a signal; in the TRACKING mode the PLL is locked onto a signal and will retain that lock through phase and frequency variations of the signal. In general, at the basic circuits/systems level, we will be concerned with the tracking (the phase-locked) mode and over what range of frequency and phase variation the PLL can track the signal. The basic behavior of the PLL can be related to measurable steady-state quantities at each stage in the PLL. For steady-state analysis sophisticated feedback theory is NOT needed. However, before we can understand loop operation we must become familiar with the individual loop components.

<sup>&</sup>lt;sup>1</sup>The material in this section follows the development of Paul H. Young, Phase-Locked Loops: A Tutorial, Session 3548, 1984 American Society for Engineering Education Annual Conference Proceedings, p.1256-1261, also P.H. Young, <u>Electronic Communications Techniques</u>, Charles Merrill Publishers, Chapter 10, 1985.

VOLTAGE CONTROLLED OSCILLATOR

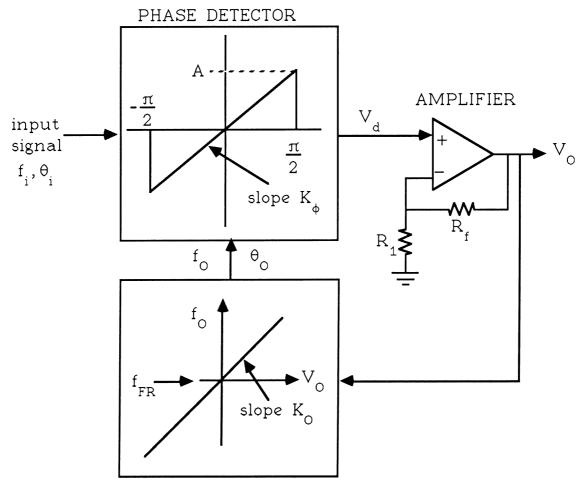

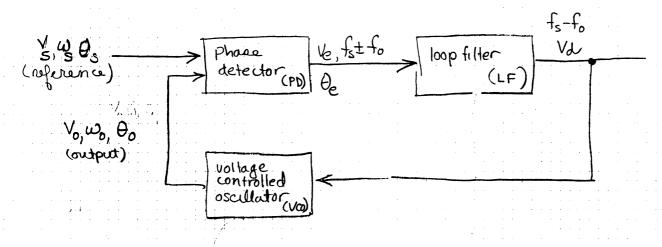

Figure 1 - Basic Phase Locked Loop Components

# LOOP COMPONENTS

The PLL shown in Figure 1 consists of a phase comparator (detector), an error signal amplifier (a differential amplifier) and a voltage controlled oscillator (VCO).

The phase detector ( $\phi$  detector) is a dc coupled mixer. In general, this behaves exactly like any other mixer producing sum and difference frequency components in its output except that its inputs and output can also have dc components. In PLL applications we are primarily concerned with the difference out. Assume that the input frequencies to the phase detector are different, the mixer will then produce sum and difference frequencies. Call the two different input frequencies  $f_1$  and  $f_0$ . The sum frequency  $f_0 + f_1$  can be removed from the mixer

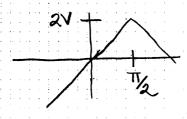

output by a low-pass filter leaving a sinusoidal signal at the difference frequency  $\Delta f = |f_0 - f_1|$ . If the input frequencies are equal, the difference frequency output will be a dc voltage proportional to the phase difference between the input signals, i.e.  $\theta_0 - \theta_1 = \theta_e$ . This can be proven by simple trigonometry. The magnitude of the dc mixer output voltage (for two identical frequencies input) will be  $v_d = K_\varphi \theta_e$  where  $K_\varphi$  is the gain slope of the phase detector curve at the operating point,  $\theta_e$  is the phase difference between the two signals and  $v_d$  is the filtered dc (in this case) mixer output voltage. For the phase detector shown in Figure 1, the gain is constant between  $-90^\circ$  and  $+90^\circ$  and is

$$K_{\phi} = \frac{A}{\frac{1}{2}\pi} = \frac{2A}{\pi} \text{ volts/radian}$$

(1)

The error signal amplifier shown in Figure 1 is a non-inverting voltage amplifier (constructed using an operational amplifier) with a gain of

$$K_{A} = 1 + \frac{R_{f}}{R_{1}} \tag{2}$$

The voltage-controlled oscillator (VCO) frequency is controlled by the input voltage  $V_O$  – the filtered output of the mixer. For simplicity, the operational amplifier is assumed capable of bipolar output and is ideal with no input voltage offset. The VCO is assumed to be at its free-running frequency  $f_{FR}$  when  $V_O = 0$ . As shown in Figure 1, the VCO characteristic is linear with slope  $K_O$  (Hz/volt) so that any change in  $V_O$  will produce a VCO output frequency change  $\Delta f_O$ .

# ACQUISITION

Initially, the VCO is free-running at  $f_{FR}$ . A signal at frequency  $f_1$  is input to the phase detector. If  $f_1 = f_{FR}$  then the loop is instantaneously locked and  $V_0 = 0$ . The definition of "locked" is that  $f_0 = f_1$  and the VCO frequency tracks  $f_1$  exactly in the steady-state; note that there can be a phase error between  $f_0$  and  $f_1$  in the locked state.

If  $f_1$  is not equal to  $f_{FR}$  and the difference between these two frequencies is within the loop bandwidth, the resulting VCO

input signal will be a (usually sinusoidally) varying signal at the difference frequency. If the resulting VCO input signal  $V_0 = V_d K_A$  is large enough to cause the VCO to shift to  $f_1$  then lock-up (acquisition) will occur. If the difference frequency is outside the loop bandwidth, acquisition may still occur by another process known as "pull-in."

Once acquisition occurs, the loop is locked and operating in the tracking mode.

# TRACKING (LOCKED)

When the PLL is locked,  $f_0 = f_1$  and the VCO input voltage required to deviate the VCO from its free-running frequency is given by

$$V_{O} = \frac{f_{1} - f_{FR}}{K_{O}} = \frac{\Delta f}{K_{O}} \tag{4}$$

But  $V_O = K_A V_d$  so that the phase detector must produce  $V_d = \Delta f/K_O K_A$ . The phase detector can do this if its input is

$$\theta_{e} = \frac{V_{d}}{K_{\phi}} = \frac{\Delta f}{K_{O} K_{A} K_{\phi}} \tag{5}$$

The phase difference between the VCO and the input signal provides the loop error signal that is required to keep the VCO tracking  $f_1$ .  $\theta_e$  is called the STATIC (steady-state) PHASE ERROR and  $K_L = K_O K_A K_{\varphi}$  is called the loop gain. This is a very important result – the PLL VCO is at the exact same frequency as the input signal but there is a phase difference between the two signals. Equation (5) with loop gain  $K_L$  yields the fundamental relationship for the steady-state PLL

$$\theta_{e} = \frac{\Delta f}{K_{L}} \tag{6}$$

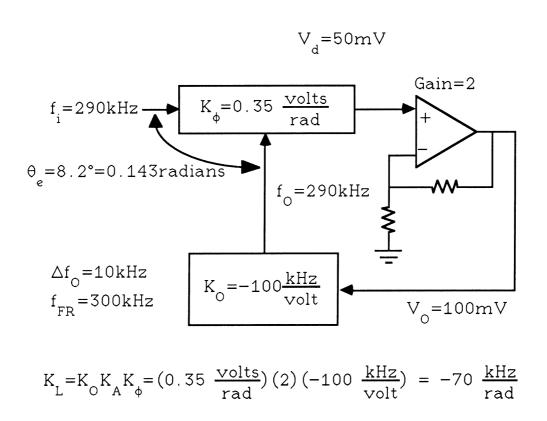

Figure 2 - Commercial PLL (NE565) in Tracking Mode Locked to 290 kHz Input Signal

To illustrate the utility of this model Figure 2 shows typical loop parameters for the most popular PLL integrated circuit, the NE 565. The voltage values that should be measured at each point in the system for  $\Delta f=10\,\mathrm{kHz}$  are also shown. The analysis starts at the VCO with the question "What must  $V_O$  be in order to keep  $f_O=f_1?$ " Once you have answered this question using  $\Delta f=K_OV_O,\ V_d$  is determined and the static phase error is specified. Basically, you must evaluate Equation (6) every time you solve a PLL problem.

# HOLD-IN RANGE AND LOSS OF LOCK

Once locked, the VCO tracks slow changes in  $f_{in}$  and  $V_{0}(t)$  is an exact replica of  $f_{1}$  deviations as long as  $\Delta f$  remains well within the loop's bandwidth and the system remains linear. This is the basis for PLLs in linear FM demodulation, i.e. stereo tuners. Given the modulation waveform m(t) and the FM peak deviation,  $V_{0}(t)$  can be determined from Equation (4).

The hold-in range is the total frequency range over which the loop can maintain phase lock. It can be predicted from the loop component characteristics. Typically, the operational amplifier saturation level and the VCO control range far exceed phase detector limitations. Notice the particular phase detector characteristic of Figure 1. This triangular phase detector characteristic is typical of phase detectors implemented with EXCLUSIVE-OR gates. A similar characteristic, but with a sinusoidal curve, is typical of analog multipliers. A saw-tooth characteristic with a  $\theta_e$  range of up to  $2\pi$  can be realized with edge-triggered flip-flops.

As the astute reader might note, PLLs can incorporate digital integrated circuits which makes PLLs ideal candidates for an all-digital implementation. In fact, all-digital PLLs are available commercially (the CD4046) and software PLLs have been implemented.

The total range over which the loop can maintain phase lock is limited to the maximum phase detector output,  $V_d(max) = \pm A$ . Thus, a frequency variation for which the loop error  $\theta_e$  exceeds  $\pm \pi/2$  will result in loss of lock.

From Equation (6) with  $\Delta f_H = f_i(max) - f_i(min)$

$$\Delta f_{H} = \pi K_{L} \tag{7}$$

is the total Hold-In frequency range. The loop of Figure 2 will maintain lock for input frequencies down to 190 kHz and up to 410 kHz before loss of lock occurs. Also, noise in the loop or ringing in an under-damped second-order loop that causes  $V_{\rm O}$  to exceed  $\pm 110\,\rm kHz/K_{\rm O}=\pm 1.1$  volts peak, will cause a loss of lock until the transient subsides to within the acquisition range of the system.

# FREQUENCY RESPONSE AND BANDWIDTH

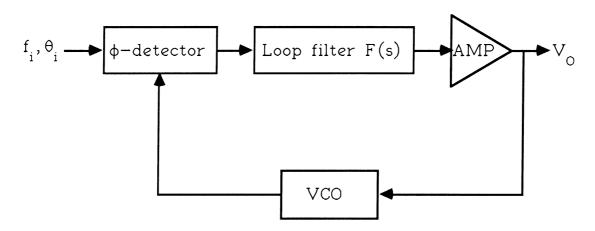

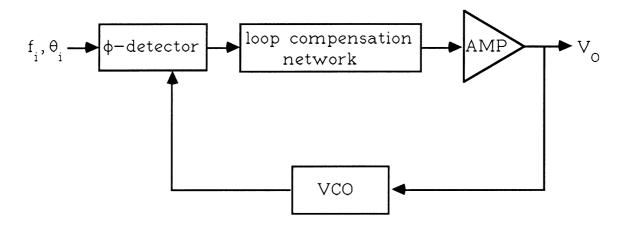

The PLL of Figure 3 will be used to illustrate the frequency response and dynamic behavior for a typical application – demodulation of analog FM and digital FSK (Frequency Shift Keyed) signals. The results have wide applications in PLL design and analysis.

Figure 3 - PLL Block Diagram

(some typical loop parameters are shown)<sup>2</sup>

When used as a demodulator, the PLL must be designed for an appropriate frequency response and bandwidth. The bandwidth and response of the loop to sudden changes of the input frequency or phase (step response) are determined by the use of Bode plots and well established reference data and graphs. Such simple graphical techniques allow the design of phase-locked systems including the loop compensation necessary for specific applications.

The Bode plot of the open-loop gain is based upon the fact that the VCO transfer function (see Figure 1) is that of an integrator<sup>3</sup>. The phase detector and amplifier are presumed to be broadband for at least an order of magnitude above the uncompensated loop bandwidth.

3The VCO frequency can be written as

$$f_0 = \frac{1}{2\pi} \frac{d\theta_0(t)}{dt}$$

Consequently.

$$\theta_{o}(t) = 2\pi \int f_{o}dt = 2\pi f_{o}t + \theta_{o}$$

for a constant fo. For a linear VCO characteristic,  $\Delta f_0 = K_0 V_0(t)$  ,  $\Delta f_0 = K_0 V_0(t)$  and the instantaneous VCO phase is

$$\theta_{O}(t) = 2\pi f_{O}t + 2\pi K_{O}\int V_{O}(t) dt + \theta_{O}$$

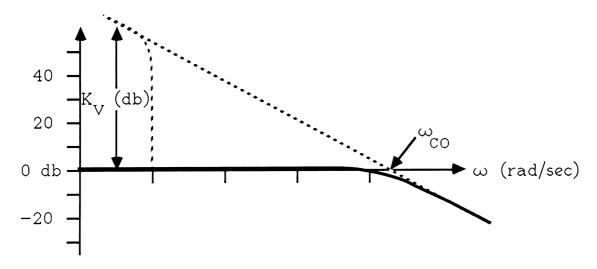

Figure 4 - Open-loop (dashed line) and Closed-Loop Bode Plot for Uncompensated Loop

Figure 4 shows the open-loop (dashed) and closed loop frequency response for the uncompensated PLL of Figure 3. The required loop gain for a given application is determined primarily from the allowable steady-state error based upon hold-in range and minimum bandwidth. The closed loop frequency response indicates that, compared to a typical voltage amplifier feedback system, there is 100% feedback for the PLL. The closed loop response could also be labeled  $V_0(\omega)$  since it follows the relative output amplitude versus frequency for the input signal frequency modulated by a sinusoid of frequency  $\omega_0$ . Notice that the sinusoidal response is flat for low frequencies, is down 3 db at  $\omega_{CO}$  (the loop crossover frequency), and rolls off at 6 db/octave for high loop frequencies. The uncompensated PLL is seen to behave much like a 1st order low-pass filter that tracks an input carrier hence, its application as a "tracking filter." Finally, you must realize that the VCO will track frequencies above as well as below its free-running frequency so, for noise bandwidth considerations, the Bode plots of Figure 4 are one-sided only.

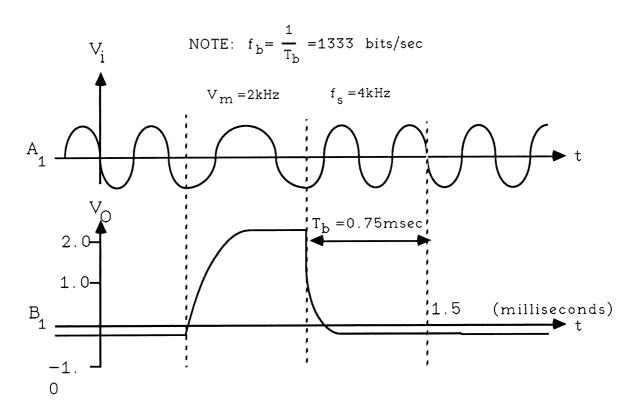

Figure 5 - Frequency Shift Key PLL Demodulation

A. FSK Input to PLL B. Demodulated Output

The response of the uncompensated PLL of Figure 3 to a digital FSK signal is shown in Figure 5. Figure 5(a) shows the 1333 bit/sec baud rate FSK signal and Figure 5(b) shows the demodulated output  $V_{\rm O}(t)$ . Since the VCO can be used to modulate such an FSK signal, the PLL integrated circuit is usually a vital component of data MODEMs. Notice that in Figure 5(b) the first-order low-pass filter type of response to the input frequency step change. The time constant is  $\tau=1/K_{\rm V}$  because the closed loop 3 db frequency and open loop crossover frequencies are both equal to  $K_{\rm V}$  for the uncompensated PLL.

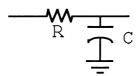

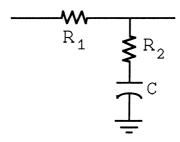

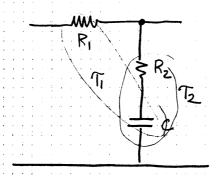

A. Lag compensation network

B. Lead-lag compensation network

Figure 6 - Block Diagram of the Compensated PLL

For many applications, the first order system response is inadequate or undesirable. In this case, the loop can be made second-order by inserting an RC lag or lead-lag network at the output of the phase detector. These compensation networks (filters) are shown in Figure 6. Also shown in Figure 6 is the block diagram for the compensated PLL. For lag compensation, the location of the RC corner frequency,

$$\omega_{\rm C} = \frac{1}{\rm RC} \tag{9}$$

determines the actual amount by which the phase margin (PM) is reduced, thus reducing the loop damping factor  $\delta$ . The RC corner frequency and phase margin are related by

Phase margin = 180° -[90°+tan<sup>-1</sup>(

$$\frac{\omega_{CO}}{\omega_{C}}$$

)] (10)

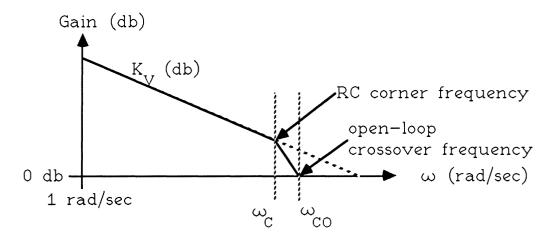

where  $\omega_{CO}$  is the open-loop crossover frequency (See Figure 7) and the 90° represents the phase lag due to the integrating effect of the VCO.

Figure 7 - Bode Plot for Lag Compensated PLL

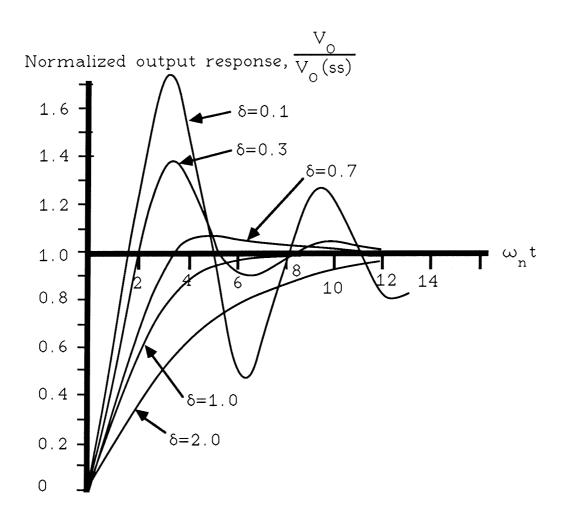

The loop damping factor can be determined from the universal second-order system curves of Figure 8 using the calculated value of phase margin, or it can be calculated directly from

$$\delta = \frac{1}{2} \sqrt{\frac{\omega_{\rm C}}{K_{\rm V}}} \tag{11}$$

when lag compensation is used. Equation (10) gives the Bode asymptotic approximation to the phase margin. The actual phase margin is greater than that calculated and is determined from the closed loop crossover frequency.

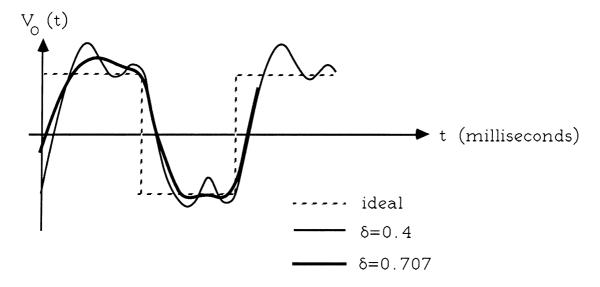

Figure 8 - Second-order loop response to step-change in input frequency.

Equation (11) clearly indicates how loop damping is determined by the relative relationship of  $\omega_C$  to the uncompensated loop crossover frequency. As determined from Equation (11), by setting the RC time constant so that  $\omega_C$  is one octave above  $K_V$ , the loop will be compensated for  $\delta=0.707$ . This is optimum damping for most PLL applications.

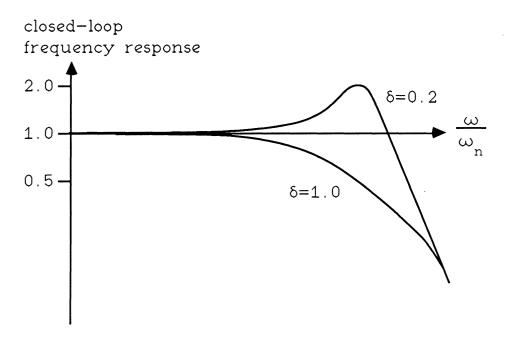

Loop compensation changes the first-order PLL system to a second-order system. The closed loop frequency response and bandwidth are no longer as simple as that shown in Figure 4. For second-order systems, the universal curves of Figure 9 can be used.

Figure 9 - Closed-loop response of Second Order PLL

When using the curves of Figures 8 and 9, the time axis must be de-normalized for the particular loop dynamics by the use of  $\omega_n$ , the undamped natural frequency of the loop. This is calculated for the PLL with lag compensation from

$$\omega_{\rm n} = \sqrt{\omega_{\rm c} K_{\rm V}} \tag{12}$$

Equation (12) indicates that the undamped frequency of the loop oscillations is the geometric mean of the loop filter corner frequency and the loop gain (in radians/second).

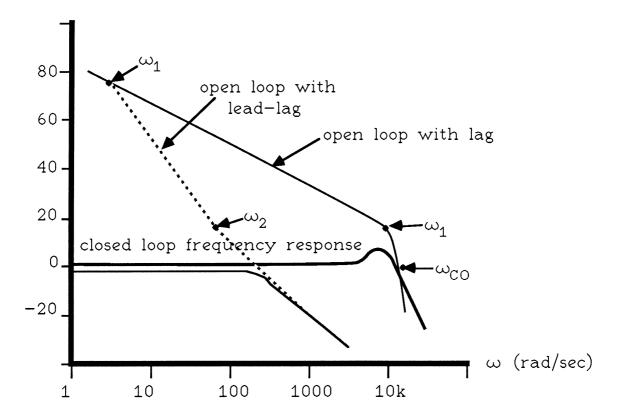

The FM/FSK demodulator of Figure 3 with a lag compensation network consisting of  $R=3\,k\Omega$  and  $C=0.068\,\mu F$  was analyzed using the techniques described above. Figure 10 shows the open and closed loop frequency response. Figure 11 shows the step response for input frequency shifts of 3.5 kHz representing FSK demodulation of 1,0 bits being sent at a baud rate of 470 bits/second.

Figure 10 - Bode plot of Figure 3 loop with two types of frequency compensation

Figure 11 - Response of second-order loop to input frequency step.

The response for  $\delta=0.707$  is also shown as the dotted line in Figure 11. Note that the horizontal axis of Figure 8 is

denormalized with Equation 12 and the vertical axis is denormalized with

$$V_{O(\text{steady state})} = \frac{\Delta f}{K_{O}}$$

(13)

Figure 8 also allows for the determination of percentage overshoot and settling time.

# LEAD-LAG COMPENSATION

Lag compensation allows the designer to set the loop gain and damping (amount of overshoot, ringing and settling time) independently. However, the system bandwidth is fixed without alteration once the above parameters are set.

If a lead-lag network is used for loop compensation, all three system parameters – loop gain, damping and bandwidth – can be set independently. Resistor  $R_2$  with capacitor C of Figure 6b provides a "zero" of leading phase shift that improves the phase margin at the same time that the loop (one-sided) bandwidth is fixed at B in Figure 10.

The procedure for lead-lag compensation for  $\delta=0.707$  is as follows: (refer to the dotted lines in Figure 10). The uncompensated open loop Bode plot is made. Then the desired bandwidth B is marked on the 0 db axis. A 6 db/octave line is drawn through the bandwidth point and a point  $\omega_2=\frac{1}{2}B$  is placed on this line at the +6 db open-loop gain. This will set the damping factor to  $\delta=0.707$  for a high gain loop. A -12 db/octave line is drawn through  $\omega_2$  until it intersects the uncompensated Bode plot line at  $\omega_1$ . With capacitor C arbitrarily chosen,  $R_2$  is determined from

$$\omega_2 = \frac{1}{R_2 C} \tag{15}$$

and

$$\omega_1 = \frac{1}{(R_1 + R_2)C} \tag{16}$$

will yield  $R_1$  where

$$R_1 = \frac{1}{\omega_1 C} - R_2$$

The loop is thus compensated for  $\delta=0.707$  with bandwidth B and loop gain  $K_V$ . The exact values for  $\delta$  and  $\omega_n$  (used to denormalize the universal second-order response curves), for the lead-lag compensated PLL are

$$\delta = \frac{1}{2}\omega_{n}\left(\frac{1}{\omega_{2}} + \frac{1}{K_{V}}\right) \tag{17}$$

and

$$\omega_{\rm n} = \sqrt{\frac{K_{\rm V}\omega_1\omega_2}{\omega_1 + \omega_2}} \tag{18}$$

or for  $\omega_2 >> \omega_1$ ,

$$\omega_{\rm n} = \sqrt{K_{\rm V}\omega_{\rm 2}}$$

# PHASE-LOCKED LOOP DESIGN FUNDAMENTALS

Prepared by

Garth Nash

Applications Engineering

The fundamental design concepts for phase locked loops implemented with integrated circuits are outlined. The necessary equations required to evaluate the basic loop performance are given in conjunction with a brief design example.

Reprintéd with Permission of Motorola Inc. Allrights Reserved.

**MOTOROLA Semiconductor Products Inc.**

# PHASE-LOCKED LOOP DESIGN FUNDAMENTALS

#### INTRODUCTION

The purpose of this application note is to provide the electronic system designer with the necessary tools to design and evaluate Phase Locked Loops (PLL) configured with integrated circuits. The majority of all PLL design problems can be approached using the Laplace transform technique. Therefore, a brief review of Laplace is included to establish a common reference with the reader. Since the scope of this article is practical in nature all theoretical derivations have been omitted hoping to simplify and clarify the content. A bibliography is included for those who desire to pursue the theoretical aspect.

#### PARAMETER DEFINITION

The Laplace Transform permits the representation of the time response f(t) of a system in the complex domain F(s). This response is twofold in nature in that it contains both the transient and steady state solutions. Thus, all operating conditions are considered and evaluated. The Laplace transform is valid only for positive real time linear parameters; thus, its use must be justified for the PLL which includes both linear and nonlinear functions. This justification is presented in Chapter Three of Phase Lock Techniques by Gardner. 1

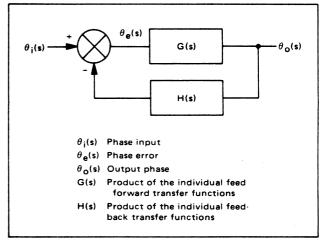

The parameters in Figure 1 are defined and will be used throughout the text.

FIGURE 1 - Feedback System

Using servo theory, the following relationships can be obtained.  $\!\!\!\!\!^{2}$

$$\theta_{e}(s) = \frac{1}{1 + G(s) H(s)} \theta_{i}(s)$$

(1)

$$\theta_{O}(s) = \frac{G(s)}{1 + G(s) H(s)} \theta_{i}(s)$$

(2)

These parameters relate to the functions of a PLL as shown in Figure 2.

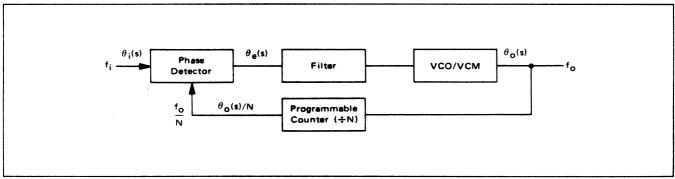

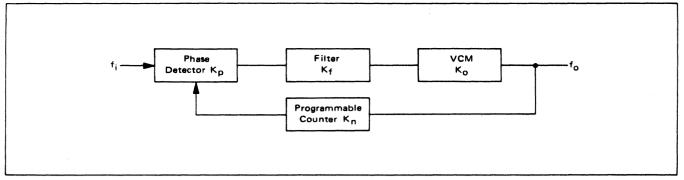

FIGURE 2 - Phase Locked Loop

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

The phase detector produces a voltage proportional to the phase difference between the signals  $\theta_i$  and  $\theta_0/N$ . This voltage upon filtering is used as the control signal for the VCO/VCM (VCM - Voltage Controlled Multivibrator).

Since the VCO/VCM produces a frequency proportional to its input voltage, any time variant signal appearing on the control signal will frequency modulate the VCO/VCM. The output frequency is

$$f_0 = N f_i \tag{3}$$

during phase lock. The phase detector, filter, and VCO/VCM compose the feed forward path with the feedback path containing the programmable divider. Removal of the programmable counter produces unity gain in the feedback path (N = 1). As a result, the output frequency is then equal to that of the input.

Various types and orders of loops can be constructed depending upon the configuration of the overall loop transfer function. Identification and examples of these loops are contained in the following two sections.

#### TYPE - ORDER

These two terms are used somewhat indiscriminately in published literature, and to date there has not been an established standard. However, the most common usage will be identified and used in this article.

The type of a system refers to the number of poles of the loop transfer function G(s) H(s) located at the origin. Example:

let

$$G(s) H(s) = \frac{10}{s(s+10)}$$

(4)

This is a type one system since there is only one pole at the origin.

The <u>order</u> of a system refers to the highest degree of the polynomial expression

1 + G(s) H(s) =

$$0 \triangle C.E.$$

(5)

which is termed the <u>Characteristic Equation</u> (C.E.). The roots of the characteristic equation become the closed loop poles of the overall transfer function. Example:

$$G(s) H(s) = \frac{10}{s(s+10)}$$

(6)

ther

$$1 + G(s)H(s) = 1 + \frac{10}{s(s+10)} = 0$$

(7)

therefore

$$C.E. = s(s + 10) + 10$$

(8)

C.E. =

$$s^2 + 10s + 10$$

(9)

which is a second order polynomial. Thus, for the given G(s) H(s), we obtain a type 1 second order system.

## **ERROR CONSTANTS**

Various inputs can be applied to a system. Typically these include step position, velocity, and acceleration. The response of type 1, 2, and 3 systems will be examined with the various inputs.

$\theta_e(s)$  represents the phase error that exists in the phase detector between the incoming reference signal  $\theta_i(s)$  and the feedback  $\theta_O(s)/N$ . In evaluating a system,  $\theta_e(s)$  must be examined in order to determine if the steady state and transient characteristics are optimum and/or satisfactory. The transient response is a function of loop stability and is covered in the next section. The steady state evaluation can be simplified with the use of the final value theorem associated with Laplace. This theorem permits finding the steady state system error  $\theta_e(s)$  resulting from the input  $\theta_i(s)$  without transforming back to the time domain.<sup>3</sup>

Simply stated

$$\operatorname{Lim} [\theta(t)] = \operatorname{Lim} [s \, \theta_{e}(s)] \tag{10}$$

$$t \to \infty \qquad s \to o$$

Where

$$\theta_{e}(s) = \frac{1}{1 + G(s) H(s)} \theta_{i}(s) \tag{11}$$

The input signal  $\theta_i(s)$  is characterized as follows:

Step position:

$$\theta_i(t) = C_p \quad t \ge 0$$

(12)

Or, in Laplace notation:

$$\theta_i(s) = \frac{C_p}{s}$$

(13)

where  $C_p$  is the magnitude of the phase step in radians. This corresponds to shifting the phase of the incoming reference signal by  $C_p$  radians:

Step velocity:

$$\theta_i(t) = C_v t \ t \ge 0$$

(14)

Or, in Laplace notation:

$$\theta_i(s) = \frac{C_V}{s^2}$$

(15)

where  $C_V$  is the magnitude of the rate of change of phase in radians per second. This corresponds to inputing a frequency that is different than the feedback portion of the VCO frequency. Thus,  $C_V$  is the frequency difference in radians per second seen at the phase detector.

Step acceleration:

$$\theta_i(t) = C_a t^2 \ t \ge 0$$

(16)

Or, in Laplace notation:

$$\theta_i(s) = \frac{2 C_a}{s^3}$$

(17)

C<sub>a</sub> is the magnitude of the frequency rate of change in radians per second per second. This is characterized by a time variant frequency input.

Typical loop G(s) H(s) transfer functions for types 1, 2, and 3 are:

Type 1

$$G(s) H(s) = \frac{K}{s(s+a)}$$

(18)

Type 2 G(s) H(s) =

$$\frac{K(s+a)}{s^2}$$

(19)

Type 3 G(s) H(s) =

$$\frac{K(s+a)(s+b)}{s^3}$$

(20)

The final value of the phase error for a type 1 system with a step phase input is found by using Equations 11 and 13.

$$\theta_{e}(s) = \left(\frac{1}{1 + \frac{K}{s(s+a)}}\right) \left(\frac{C_{p}}{s}\right)$$

$$=\frac{(s+a)^{C}p}{(s^{2}+as+K)}$$

(21)

$$\theta_e(t=\infty) = \lim_{s \to 0} \left[ s \left( \frac{s+a}{s^2 + as + K} \right) C_p \right] = 0$$

(22)

Thus the final value of the phase error is zero when a step position (phase) is applied.

Similarly applying the three inputs into type 1, 2 and 3 systems and utilizing the final value theorem, the following table can be constructed showing the respective steady state phase errors.

TABLE I - Steady State Phase Errors for Various System Types

|                      | Type 1                    | Type 2   | Туре 3 |

|----------------------|---------------------------|----------|--------|

| Step<br>Position     | Zero                      | Zero     | Zero   |

| Step<br>Velocity     | Constant                  | Zero     | Zero   |

| Step<br>Acceleration | Continually<br>Increasing | Constant | Zero   |

A zero phase error identifies phase coherence between the two input signals at the phase detector.

A constant phase error identifies a phase differential between the two input signals at the phase detector. The magnitude of this differential phase error is proportional to the loop gain and the magnitude of the input step.

A continually increasing phase error identifies a time rate change of phase. This is an unlocked condition for the phase loop.

Using Table I the system type can be determined for specific inputs. For instance, if it is desired for a PLL to track a reference frequency (step velocity) with zero phase error, a minimum of type 2 is required.

# **STABILITY**

The root locus technique of determining the position of system poles and zeroes in the s-plane is often used to graphically visualize the system stability. The graph or plot illustrates how the closed loop poles (roots of the character-

istic equation) vary with loop gain. For stability all poles must lie in the left half of the s-plane. The relationship of the system poles and zeroes then determine the degree of stability. The root locus contour can be determined by using the following guidelines.<sup>2</sup>

- Rule 1 The root locus begins at the poles of G(s) H(s) (K = 0) and ends at the zeroes of G(s) H(s)  $(K = \infty)$ . Where K is loop gain.

- Rule 2 The number of root loci branches is equal to the number of poles or number of zeroes, whichever is greater. The number of zeroes at infinity is the difference between the number of finite poles and finite zeroes of G(s) H(s).

- Rule 3 The root locus contour is bounded by asymptotes whose angular position is given by

$$\frac{(2n+1)}{\#P - \#Z} \pi; \ n = 0, 1, 2, \dots$$

(23)

Where #P (#Z) is the number of poles (zeroes).

Rule 4 - The intersection of the asymptotes is positioned at the center of gravity C. G.

$$C.G. = \frac{\Sigma P - \Sigma Z}{\# P - \# Z} \tag{24}$$

Where  $\Sigma P(\Sigma Z)$  denotes the summation of the poles (zeroes).

- Rule 5 On a given section of the real axis, root loci may be found in the section only if the #P + #Z to the right is odd.

- Rule 6 Breakaway points from negative real axis is given by:

$$\frac{dK}{ds} = 0 \tag{25}$$

Again where K is the loop gain variable factored from the characteristic equation.

Example:

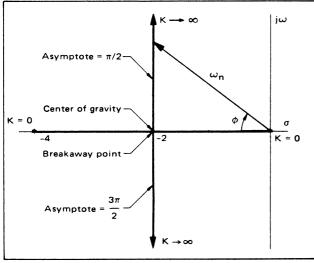

The root locus for a typical loop transfer function is found as follows:

G(s) H(s) =

$$\frac{K}{s(s+4)}$$

(26)

The root locus has two branches (Rule 2) which begin at s = 0 and s = -4 and ends at the two zeroes located at infinity (Rule 1). The asymptotes can be found according to Rule 3. Since there are two poles and no zeroes the equation becomes:

$$\frac{2n+1}{2} \pi = \begin{cases} \frac{\pi}{2} & \text{for } n=0\\ \frac{3\pi}{2} & \text{for } n=1 \end{cases}$$

(27)

The position of the intersection according to the Rule 4 is:

$$s = \frac{\Sigma P - \Sigma Z}{\# P - \# Z} = \frac{(-4 - 0) - (0)}{2 - 0}$$

$$s = -2 \tag{28}$$

The breakaway point as defined by Rule 6 can be found by first writing the characteristic equation.

C.E. = 1 + G(s) H(s) = 0

= 1 +

$$\frac{K}{s(s+4)}$$

= s<sup>2</sup> + 4s + K = 0 (29)

Now solving for K yields

$$K = -s^2 - 4s$$

(30)

Taking the derivative with respect to s and setting it equal to zero then determines the breakaway point.

$$\frac{dK}{ds} = \frac{d}{ds} (-s^2 - 4s) \tag{31}$$

$$\frac{dK}{ds} = -2s - 4 = 0 {(32)}$$

or

$$s = -2 \tag{33}$$

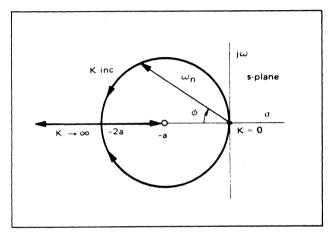

is the point of departure. Using this information, the root locus can be plotted as in Figure 3.

This second order characteristic equation given by Equation 29 has been normalized to a standard form<sup>2</sup>

$$s^2 + 2\zeta \omega_n s + \omega_n^2$$

(34)

where the damping ratio  $\zeta = \cos \phi$  (0°  $\leq \phi \leq$  90°) and  $\omega_n$  is the natural frequency as shown in Figure 3.

FIGURE 3 - Type 1 Second Order Root Locus Contour

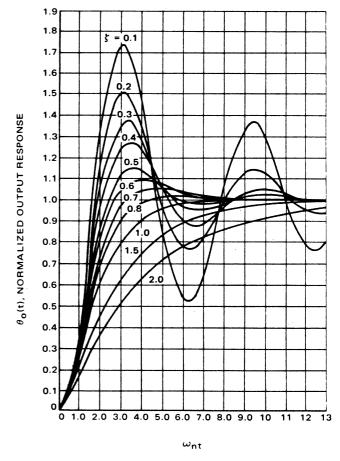

The response of this type 1, second order system to a step input is shown in Figure 4. These curves represent the phase response to a step position (phase) input for various damping ratios. The output frequency response as a function of time to a step velocity (frequency) input is also characterized by the same set of figures.

FIGURE 4 - Type 1 Second Order Step Response

The overshoot and stability as a function of the damping ratio  $\zeta$  is illustrated by the various plots. Each response is plotted as a function of the normalized time  $\omega_n t$ . For a given  $\zeta$  and a lock-up time t, the  $\omega_n$  required to achieve the desired results can be determined. Example:

Assume

$$\zeta = 0.5$$

error  $< 10\%$

for t  $> 1$  ms

From  $\zeta$  = 0.5 curve the error is less than 10% of final value for all time greater than  $\omega_n t$  = 4.5. The required  $\omega_n$  can then be found by:

$$\omega_{\rm n}t = 4.5 \tag{35}$$

or

$$\omega_{\rm n} = \frac{4.5}{1} = \frac{4.5}{0.001} = 4.5 \text{ k rad/s}$$

(36)

ζ is typically selected between 0.5 and 1 to yield optimum overshoot and noise performance.

Example:

Another common loop transfer function takes the form

$$G(s) H(s) = \frac{(s+a)k}{s^2}$$

(37)

This is a type 2 second order system. A zero is added to provide stability. (Without the zero the poles would move along the  $j\omega$  axis as a function of gain and the system would at all times be oscillatory in nature.) The root locus shown in Figure 5 has two branches beginning at the origin with one asymptote located at 180 degrees. The center of gravity is s=a; however, with only one asymptote there is no intersection at this point. The root locus lies on a circle centered at s=-a and continues on all portions of the negative real axis to left of the zero. The breakaway point is s=-2a.

FIGURE 5 - Type 2 Second Order Root Locus Contour

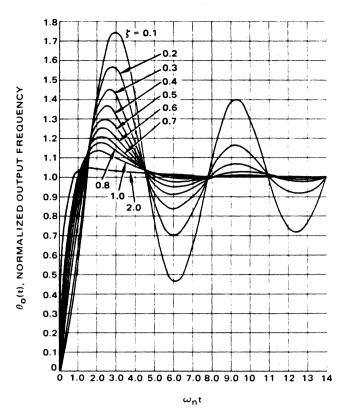

The respective phase or output frequency response of this type 2 second order system to a step position (phase) or velocity (frequency) input is shown in Figure 6. As illustrated in the previous example the required  $\omega_n$  can be determined by the use of the graph when  $\zeta$  and the lock up time are given.

#### **BANDWIDTH**

The -3 dB bandwidth of the PLL is given by

$$\omega_{-3} dB = \omega_n \left( 1 - 2 \zeta^2 + \sqrt{2 - 4 \zeta^2 + 4 \zeta^4} \right)^{1/2}$$

(38)

for a type 1 second order<sup>4</sup> system, and by

$$\omega_{-3 \text{ dB}} = \omega_{\text{n}} \left( 1 + 2 \zeta^2 + \sqrt{2 + 4 \zeta^2 + 4 \zeta^4} \right)^{\frac{1}{2}}$$

(39)

for a type 2 second order 1 system.

## PHASE-LOCKED LOOP DESIGN EXAMPLE

The design of a PLL typically involves determining the type of loop required, selecting the proper bandwidth, and establishing the desired stability. A fundamental approach

FIGURE 6 - Type 2 Second Order Step Response

to these design constraints is now illustrated. It is desired for the system to have the following specifications:

| Output frequency                | 2.0 MHz to 3.0 MHz |  |

|---------------------------------|--------------------|--|

| Frequency steps                 | 100 kHz            |  |

| Phase coherent frequency output | _                  |  |

| Lock-up time between            |                    |  |

| channels                        | 1 ms               |  |

| Overshoot                       | < 20%              |  |

NOTE: These specifications characterize a system function similar to a variable time base generator or a frequency synthesizer.

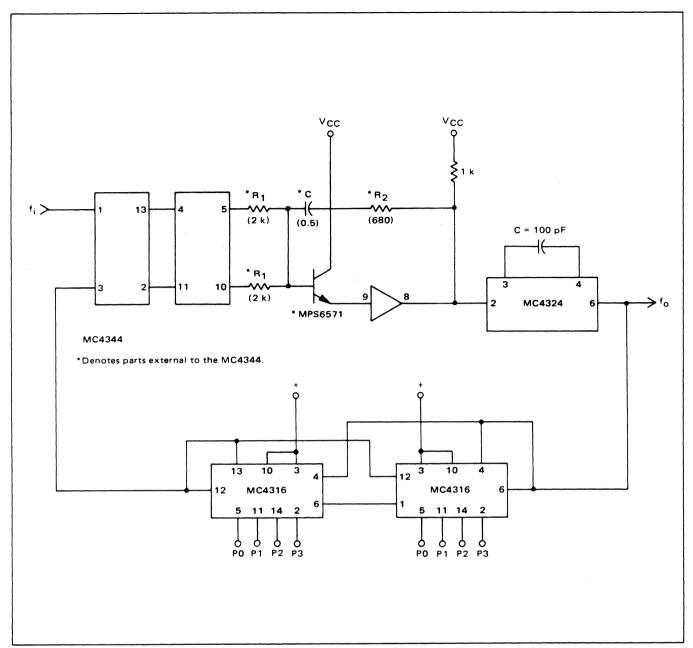

From the given specifications the circuit parameters shown in Figure 7 can now be determined.

The devices used to configure the PLL are:

Frequency-Phase Detector MC4044/4344

Voltage Controlled

Multivibrator (VCM) MC4024/4324

Programmable Counter MC4016/4316

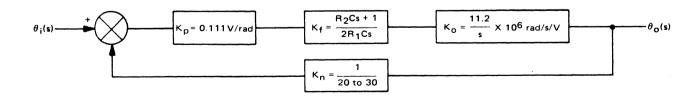

The forward and feedback transfer functions are given by:

$$G(s) = K_p K_f K_0 H(s) = K_n (40)$$

where

$$K_n = 1/N$$

(41)

FIGURE 7 - Phase Locked Loop Circuit Parameters

The programmable counter divide ratio  $K_n$  can be found from Equation 3.

$$N_{min} = \frac{f_{o min}}{f_i} = \frac{f_{o min}}{f_{step}} = \frac{2 MHz}{100 kHz} = 20$$

(42)

$$N_{\text{max}} = \frac{f_{\text{o max}}}{f_{\text{step}}} = \frac{3 \text{ MHz}}{100 \text{ kHz}} = 30$$

(43)

$$K_n = \frac{1}{20} \text{ to } \frac{1}{30}$$

(44)

A type 2 system is required to produce a phase coherent output relative to the input (see Table I). The root locus contour is shown in Figure 5 and the system step response is illustrated by Figure 6.

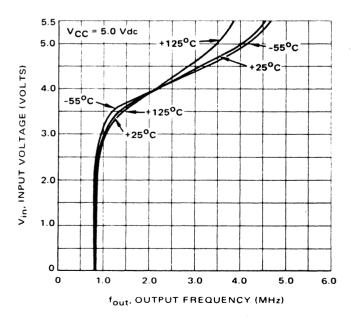

The operating range of the MC4024/4324 VCM must cover 2 MHz to 3 MHz. Selecting the VCM control capacitor according to the rules contained on the data sheet yields C = 100 pF. The desired operating range is then centered within the total range of the device. The input voltage versus output frequency is shown in Figure 8.

FIGURE 8 - MC4324 Input Voltage versus Output Frequency (100 pF Feedback Capacitor)

The transfer function of the VCM is given by

$$K_{O} = \frac{K_{V}}{s} \tag{45}$$

Where  $K_V$  is the sensitivity in radians per second per volt. From the curve in Figure 8,  $K_V$  is found by taking the reciprocal of the slope.

$$K_{V} = \frac{4 \text{ MHz} - 1.5 \text{ MHz}}{5 \text{ V} - 3.6 \text{ V}} 2\pi \text{ rad/s/V}$$

$$K_{V} = 11.2 \text{ X } 10^{6} \text{ rad/s/V}$$

(46)

Thus

$$K_{\rm O} = \frac{11.2 \times 10^6}{\rm s} \, \text{rad/s/V}$$

(47)

The s in the denominator converts the frequency characteristics of the VCM to phase, i.e., phase is the integral of frequency.

The gain constant for the MC4044/4344 phase detector is found by  $^{5}$

$$K_p = \frac{DF \text{ High - UF Low}}{2(2\pi)} = \frac{2.3 \text{ V - 0.9 V}}{4\pi} = 0.111 \text{ V/rad (48)}$$

Since a type 2 system is required (phase coherent output) the loop transfer function must take the form of Equation 19. The parameters thus far determined include  $K_p$ ,  $K_0$ ,  $K_n$  leaving only  $K_f$  as the variable for design. Writing the loop transfer function and relating it to Equation 19

G(s) H(s) =

$$\frac{K_p K_v K_n K_f}{s} = \frac{K(s+a)}{s^2}$$

(49)

Thus Kf must take the form

$$K_{f} = \frac{s+a}{s} \tag{50}$$

in order to provide all the necessary poles and zeroes for

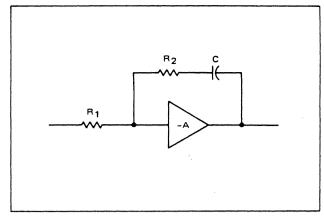

the required G(s) H(s). The circuit shown in Figure 9 yields the desired results.

Kf is expressed by

$$K_f = \frac{R_2Cs + 1}{R_1Cs} \quad \text{for large A}$$

(51)

where A is voltage gain of the amplifier.

R<sub>1</sub>, R<sub>2</sub>, and C are then the variables used to establish the overall loop characteristics.

The MC4044/4344 provides the active circuitry required to configure the filter  $K_f$ . An additional low current high  $\beta$  buffering device or FET can be used to boost the input impedance thus minimizing the leakage current from the capacitor C between sample updates. As a result longer sample periods are achievable.

Since the gain of the active filter circuitry in the MC4044/4344 is not infinite, a gain correction factor  $K_C$  must be applied to  $K_f$  in order to properly characterize the function.  $K_C$  is found experimentally to be  $K_C = 0.5$ .

$$K_{fc} = K_f K_c = 0.5 \left( \frac{R_2 C_s + 1}{R_1 C_s} \right)$$

(52)

( For large gain, Equation 51 applies. )

The PLL circuit diagram is shown in Figure 10 and its Laplace representation in Figure 11.

The loop transfer function is

$$G(s) H(s) = K_p K_{fc} K_o K_n$$

(53)

G(s) H(s) = K<sub>p</sub> (0.5)

$$\left(\frac{R_2C_s + 1}{R_1C_s}\right) \left(\frac{K_v}{s}\right) \left(\frac{1}{N}\right)$$

(54)

The characteristic equation takes the form

$$C.E. = 1 + G(s) H(s) = 0$$

$$= s^2 + \frac{0.5 \, K_p \, K_v \, R_2}{R_1 N} \, s + \frac{0.5 \, K_p \, K_v}{R_1 C N} \tag{55}$$

Relating Equation 55 to the standard form given by Equation 34

$$s^{2} + \frac{0.5 \text{ K}_{p} \text{ K}_{v} \text{ R}_{2}}{\text{R}_{1} \text{N}} s + \frac{0.5 \text{ K}_{p} \text{ K}_{v}}{\text{R}_{1} \text{CN}}$$

$$= s^{2} + 2 \zeta \omega_{n} s + \omega_{n}^{2}$$

(56)

Equating like coefficients yields

$$\frac{0.5 \text{ K}_{\text{p}} \text{ K}_{\text{V}}}{\text{R}_{1} \text{CN}} = \omega_{\text{n}}^{2} \tag{57}$$

FIGURE 9 - Active Filter Design

and

$$\frac{0.5 \text{ K}_{p} \text{ K}_{v} \text{ R}_{2}}{\text{R}_{1} \text{N}} = 2 \zeta \omega_{n}$$

(58)

With the use of an active filter whose open loop gain (A) is large  $(K_C = 1)$ , Equations 57 and 58 become

$$\frac{K_p K_v}{R_1 CN} = \omega_n^2$$

(59)

$$\frac{K_p K_v R_2}{R_1 N} = 2 \zeta \omega_{\mathbf{a}_{\mathbf{a}_{\mathbf{a}}}} \tag{60}$$

The percent overshoot and settling time are now used to determine  $\omega_n$ . From Figure 6 it is seen that a damping ratio  $\zeta=0.8$  will produce a peak overshoot less than 20% and will settle to within 5% at  $\omega_n t=4.5$ . The required lock-up time is 1 ms.

$$\omega_{\rm n} = \frac{4.5}{\rm t} = \frac{4.5}{0.001} = 4.5 \text{ k rad/s}$$

(61)

Rewriting Equation 57

$$R_1C = \frac{0.5 \text{ K}_p \text{ K}_v}{\omega_n^2 N}$$

(62)

$$=\frac{(0.5) (0.111) (11.2 \times 10^6)}{(4500)^2 (30)}$$

$$R_1C = 0.00102$$

(Maximum overshoot occurs at  $N_{max}$  which is minimum loop gain)

Let

$$C = 0.5 \mu F$$

Then  $R_1 = \frac{0.00102}{0.5 \times 10^{-6}} = 2.04 \text{ k}\Omega$

Use

$$R_1 = 2 k\Omega$$

FIGURE 10 — Circuit Diagram of Type 2 Phase Locked Loop

FIGURE 11 - Laplace Representation of Diagram in Figure 10

$R_1$  is typically selected greater than 1 k $\Omega$ . Solving for  $R_2$  in Equation 58

$$R_2 = \frac{2\xi \omega_n R_1 N}{K_p K_v (0.5)} = \frac{2\xi}{C \omega_n}$$

(63)

$$= \frac{2(0.8)}{(0.5 \times 10^{-6})(4.5 \text{ k})}$$

= 711

$$\Omega$$

use  $R_2 = 680 \Omega$

All circuit parameters have now been determined and the PLL can be properly configured.

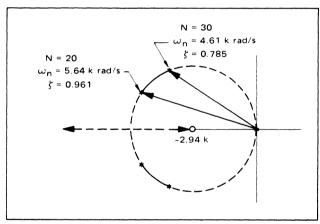

Since the loop gain is a function of the divide ratio  $K_n$ , the closed loop poles will vary is position as  $K_n$  varies. The root locus shown in Figure 12 illustrates the closed loop pole variation.

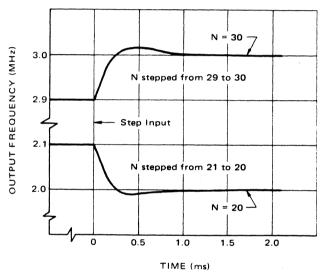

The loop was designed for the programmable counter N = 30. The system response for N = 20 exhibits a wider bandwidth and larger damping factor, thus reducing both lock-up time and percent overshoot (see Figure 14).

FIGURE 12 - Root Locus Variation

NOTE: The type 2 second order loop was illustrated as a design example because it provides excellent performance for both type 1 and 2 applications. Even in systems that do not require phase coherency a type 2 loop still offers an optimum design.

## **EXPERIMENTAL RESULTS**

Figure 13 shows the theoretical transient frequency response of the previously designed system. The curve N=30 illustrates the frequency response when the programmable counter is stepped from 29 to 30 thus producing a change in the output frequency from 2.9 MHz to 3.0 MHz. An overshoot of 18% is obtained and the output frequency is within 5 kHz of the final value one millisecond after the applied step. The curve N=20 illustrates the output fre-

quency change as the programmable counter is stepped from 21 to 20.

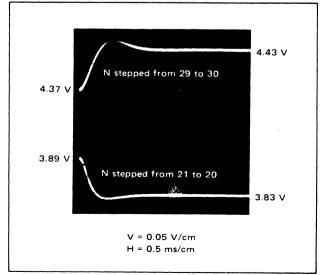

Since the output frequency is proportional to the VCM control voltage, the PLL frequency response can be observed with an oscilloscope by monitoring pin 2 of the VCM. The average frequency response as calculated by the Laplace method is found experimentally by smoothing this voltage at pin 2 with a simple RC filter whose time constant is long compared to the phase detector sampling rate but short compared to the PLL response time. With the programmable counter set at 29 the quiescent control voltage at pin 2 is approximately 4.37 volts. Upon changing the counter divide ratio to 30 the control voltage increases to 4.43 volts as shown in Figure 14. A similar transient occurs when stepping the programmable counter from 21 to 20. Figure 14 illustrates that the experimental results obtained from the configured system follows the predicted results shown in Figure 13. Linearity is maintained for phase errors less than  $2\pi$ , i.e. there is no cycle slippage at the phase detector.

FIGURE 13 - Frequency-Time Response

FIGURE 14 - VCM Control Voltage (Frequency) Transient

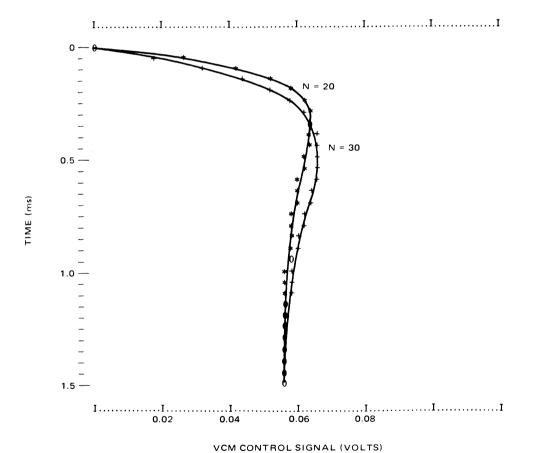

#### \*THE PARAMETERS LISTED BELOW APPLY TO THE FOLLOWING PLOT

PHASE DETECTOR GAIN CONSTANT

VCM GAIN CONSTANT

V1 = 1.12 E+7 RAD PER VOLT

FILTER INPUT RESISTOR

FILTER FEEDBACK RESISTOR

FILTER CAPACITOR

DIVIDER VALUE

REFERENCE FREQUENCY

OUTPUT FREQUENCY CHANGE

P1 = 0.111 VOLTS PER RADIAN

V1 = 1.12 E+7 RAD PER VOLT

R1 = 3900 OHMS (R1<sub>c</sub> = 2 k)

R2 = 680 OHMS

C1 = 0.5 MICROFARADS

N1-N2 = 29 - 30

REFERENCE FREQUENCY

F1 = 100000 CPS

UTPUT FREQUENCY CHANGE

F5 = 100000 CPS

PLOT OF FUNCTIONS '

(NOTE: Y(T) IS PLOTTED '+', Z(T) IS '\*', AND 'Ø' IS COMMON)

FOR T: TOP = 0 BOTTOM = 0.0015 INCREMENT = 0.00005 FOR FCTS: LEFT = 0 RIGHT = 0.12 INCREMENT = 0.002

FIGURE 15 - VCM Control Signal Transient

Figure 15 is a theoretical plot of the VCM control voltage transient as calculated by a computer program. The computer program is written with the parameters of Equations 58 and 59 (type 2) as the input variables and is valid for all damping ratios of  $\zeta \leq 1.0$ . The program prints or plots the control voltage transient versus time for desired settings of the programmable counter. The lock-up time can then be readily determined as the various parameters are varied. (If stepping from a higher divide ratio to a lower one the transient will be negative.) Figures 14 and 15 also exhibit a close correlation between the experimental and analytical results.

#### **SUMMARY**

This application note describes the basic control system techniques required for phase-locked loop design. Criteria for the selection of the optimum type of loop and methods for establishing the desired performance characteristics are presented. A design example is illustrated in a step-by-

step approach along with the comparison of the experimental and analytical results.

## **BIBLIOGRAPHY**

- Topic: Type Two System Analysis

Gardner, F. M., Phase Lock Techniques, Wiley, New York, Second Edition, 1967

- Topic: Root Locus Techniques

Kuo, B. C., Automatic Control Systems, Prentice-Hall.

Inc., New Jersey, 1962

- 3. Topic: Laplace Techniques

McCollum, P. and Brown, B., Laplace Transform Tables

and Theorems, Holt, New York, 1965

- 4. Topic: Type One System Analysis

Truxal, J.G., Automatic Feedback Control System Synthesis, McGraw-Hill, New York, 1955

- 5. Topic: Phase Detector Gain Constant

DeLaune, Jon, MTTL and MECL Avionics Digital Frequency Synthesizer, AN532

A PLL is a circuit which synchronizes an output signal (generated by an oscillator) with a reference (or input) signal in frequency and in phase. In the synchronized (locked) mode the phase error between the oscillator's output and the reference signal is very small (essentially zero). If any phase difference develops the control mechanism in the PLL acts on the oscillator to reduce the phase error to a minimum.

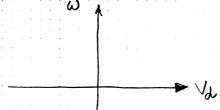

NCO

- operates at an angular frequency we determined by Va

$\omega_2(t) = \omega_f + K_o V_b(t)$

- w is the center frequency of the loop

- Ko is the VCO gain in

(phase detector or phase companator)

- compares the phase of the output signal with the phase of the reference signal send develops an output signal ve(t) which is (usually only approximately) proportional to the phase error De

$V_{e(t)} = K_{d}\theta_{e(t)}$

- Ka has units volts

output signal is usually a de component + superimpused ac component 578

loop filter

- voually a simple low pass filter

- removes the a.c. component from the PD output

How does a PLL work?

- 1. If  $w_s = w_o$  the voo must be at its center frequency. This in plies that the (the phase error) = 0 and  $V_d = 0$ . This is a stable, locked PLL.

- 2. If  $Ge \neq 0$  initially, then  $Vd \neq 0$ . This would cause the VCO to change its operating frequency  $\omega_0$  in such a way that the phase error finally vanishes. This is the acquisition mode of a PLL.

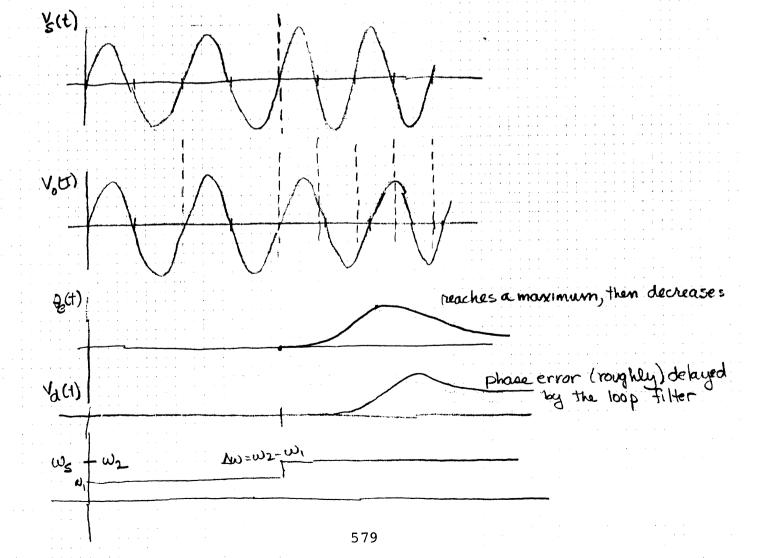

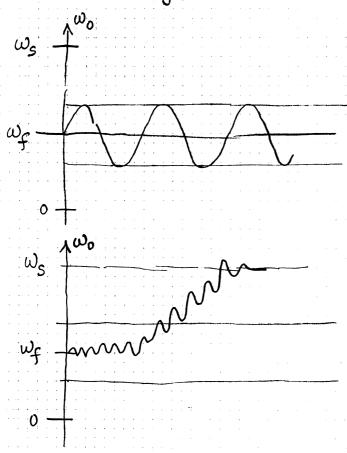

response of a fil to a step change in frequency

Assume ws suddenly jumps from w, to wz. The phase of the input signal now leads the oscillators frequency creating a phase error which increases with time. The VCO control voltage Vo(t) will also rise with a delay given by the loop filter) with time. This causes the VCO to increase its frequency which decreases the phase error. After some time interval the VCO will oscillate at a frequency that is exactly the frequency of the input signal. Depending on the type of loop filter used, the final & will either be zero or a finite value.

the VCO is now locked at a frequency W2 which is greater than W1 by DW. This means that V2(t) increased by a value  $\frac{\Delta W}{Ko}$ . If the center frequency of the input signal is frequency modulated by a low-frequency signal the output signal Va is the demodulated signal. Thus, the PLL can operate as an FM detector.

Another major application of the PLL is to remove noise from signals. Suppose Vs has a lot of noise. Then the PD output will be a random signal with some average value. If the loop filter is low enough in frequency there will be almost no noise on the loop output V<sub>d</sub>(t).

If Dw is too large the PLL will become "unlocked". The control mechanism will attempt to lack but may not be able to.

There are only several basic types of PD's., VCO's, and loop filters. which will be discursed.

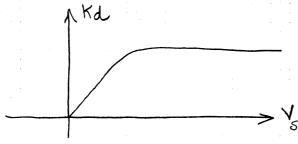

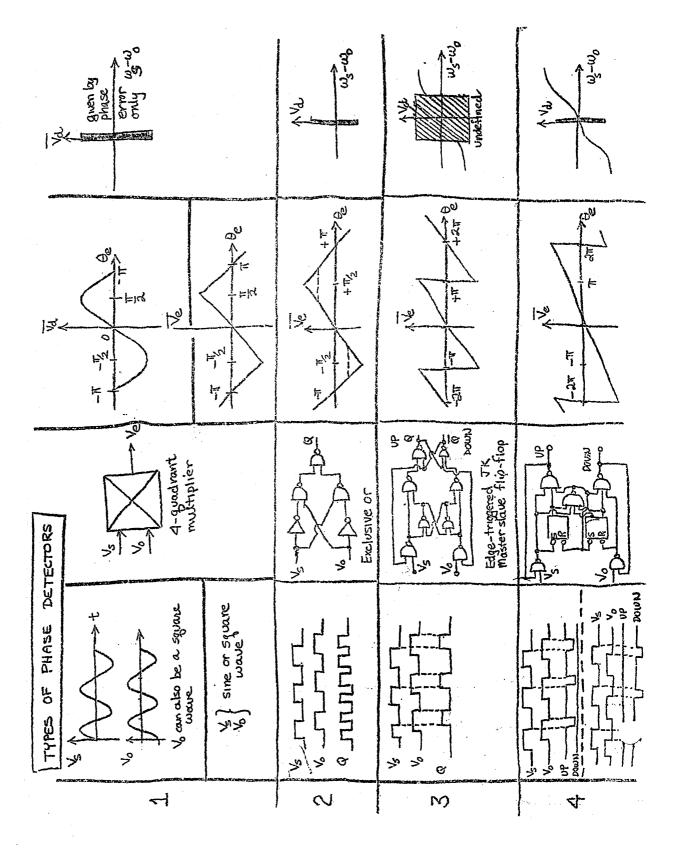

type of phase detectors

type 1 (four-quadrant multiplier)

Vs = Vs sin (wst + Os)

$N_0 = V_0 \cos (w_0 t + \theta_0)$

the your quadrant multiplier is actually a miner with output

$$= \frac{k \sqrt{s} \sqrt{t}}{2} \left[ \sin (\theta_s - \theta_0) + \sin (2 \omega_s t + \theta_s + \theta_0) \right]$$

$$= \frac{k \sqrt{s} \sqrt{t}}{2} \left[ \sin (\theta_s - \theta_0) + \sin (2 \omega_s t + \theta_s + \theta_0) \right]$$

$$= \frac{k \sqrt{s} \sqrt{t}}{2} \left[ \sin (\theta_s - \theta_0) + \sin (2 \omega_s t + \theta_s + \theta_0) \right]$$

$$= \frac{k \sqrt{s} \sqrt{t}}{2} \left[ \sin (\theta_s - \theta_0) + \sin (2 \omega_s t + \theta_s + \theta_0) \right]$$

the loop filter removes the ac component, Note that if we there is no de component.

there is no dc component.

:.

$$V_{alt} = \frac{k V_{s} V_{o}}{sin} (\theta_{s} - \theta_{o})$$

$\Theta_e = \Theta_s - \Theta_o$  and if  $\Theta_e \ll 1$  then

V<sub>d</sub>(t)

$$\approx \frac{kV_sV_o}{2} \partial_e$$

so

$$K_d = \frac{k V_s V_o}{2}$$

This is as long as Vs and Vo are small, As Vs and/or Vs increase in amplitude the type 1 PD eventually saturates.

A type 1 PD operating in the prevence of moise is an excellent futer.

Note in most PLL's the voo is a square wave so that only odd harmonics are generated and can be easily filtered.

type 2,3 and 4 PD's are digital circuits requiring analog signal processing to use them in mon-digital circuits

type 2 - XOR circuit

of in phase output is always zero.

if exactly out of phase output is a square wave at  $2w_s$ .

if N<sub>S</sub>(t) or N<sub>O</sub>(t) are not symmetrical the PD characteristic

becomes dipped

type 3 - edge Inggered JK flip-flop.

average PD output is defined by a weighted output.

mc4024

usually implemented by something ralled a change pump, i.e. an integrator with a surkhod sign.

not dependent on duty cycle frequency error regnal when luz-wolis large

type 4 - phase / frequency detector.

frequency sensitive for any (us-us)

The type of PD used is the most important cruteria in determining loop performance; however, the PLL dynamic performance is also effected by the loop filter.

The general form of a first-order LPF  $F(j\omega) = \frac{a+b(j\omega)}{c+d(j\omega)}$

jw T. POSSIBLE PLL FIRST-ORDER LOW-PASS FILTERS O-WW ACTIVE 1+ 300 F. M 1+ jw tz 1+jw(T1+Tz) 2 PASSINE 1+367 H (OK.)7 TRANSFER FUNCTION CIRCUIT F(gw) 五五 583

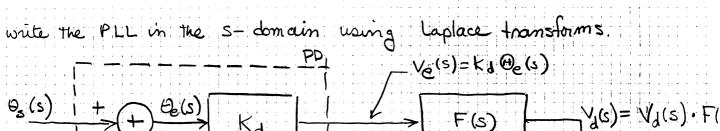

F(s) Kd

transfer functions!

$$\frac{\psi_{e(s)}}{\theta_{e(s)}} = \kappa_{d}$$

independent of frequency

$$\frac{V_{d}(s)}{V_{e}(s)} = F(s)$$

$$\frac{\theta_o(s)}{V_d(s)} = \frac{K_o}{s}$$

looks like an integrator

transfer function of the VCO

$$\omega_{s}(t) = \omega_{f} + k_{o} V_{d}(t)$$

integrate to get phase signal

$$\omega_f t + \theta_o(t) = \omega_f t + k_o \int_{6}^{V_d(\tau)} d\tau$$

applying the laplace transform

We can now write the loop transfer functions

phase transfer function

$$H(s) = \frac{\Theta_{o}(s)}{\Theta_{s}(s)}$$

$$\Theta_{o}(s) = \frac{K_{o}}{s} V_{d}(s) = \frac{K_{o}}{s} F(s) \Theta_{e}(s) = \frac{K_{o}}{s} F(s) K_{d} \left[\Theta_{s}(s) - (s)\right]$$

$$\Theta_{o}(s) \left[1 + \frac{K_{o}}{s} F(s) K_{d}\right] = \frac{K_{o}}{s} F(s) K_{d} \Theta_{s}(s)$$

$$H(s) \frac{\Theta_{o}(s)}{\Theta_{s}(s)} = \frac{K_{o}K_{d} F(s)}{s + K_{o}K_{d} F(s)}$$

error transfer function  $H_{e}(s) = \frac{\Theta_{e}(s)}{\Theta_{n}(s)}$

$$H_e(s) = \frac{\Theta_e(s)}{\Theta_o(s)}$$

$$\Theta_{e}(s) = \Theta_{s}(s) - \Theta_{o}(s) = \frac{\Theta_{o}(s)}{H(s)} - \Theta_{o}(s) = \Theta_{o}(s) \left[ \frac{I - H(s)}{H(s)} \right]$$

$$He(s) = \frac{\Theta_{e}(s)}{\Theta_{o}(s)} = \frac{1 - H(s)}{1 - H(s)} = \frac{1 - K_{o} K_{d} F(s)}{s + K_{o} K_{d} F(s)} = \frac{s}{s + K_{o} K_{d} F(s)}$$

$$S + K_{o} K_{d} F(s)$$

$$S + K_{o} K_{d} F(s)$$

We define the order of a PLL = order of loop filter +1 because the order of the denominators of Hs and He are of that order. For example, if F(s) = 95 which is first order then both H(s) and He(s) ~ 1 1.e second order theory of the linear PLL:

linear means that the PD is linear, i.e. type 1 The PLL control system is not linear

tracking can be simplified to a linear system acquisition is NEVER lineau.

represent input signals as phase signals

$$v_s(t) = V_s \sin \left[ \omega_s t + \theta_s(t) \right]$$

phase step

$$\theta = \begin{cases} 0 & t \leq 0 \\ \Delta \Phi & t > 0 \end{cases}$$

$\Theta_{1}(t) = \Delta \underline{\Phi} u(t)$

this is phase modulation

frequency step

sin [wot] t≤0 sin [wft + Dwt] t>0 { friquency step

$\therefore \theta_{s}(t) = \Delta \omega t$

the phase signal is a ramp

in general,

$$\omega_s(t) = \omega_r t + \Delta \omega t$$

where  $\Delta \omega = 2(\Delta \omega)$

or sin S[ω<sub>t</sub> + Δω τ ] dτ

$\theta_{s}(t) = \int (\Delta \omega) \tau d\tau = (\Delta \omega) \frac{t^{2}}{2}$

in its most general farm.

we used a sine and a cosine because a type 1 PD has an intrinsic phase shift of IT (90°) between the reference and output signals. Use of a sine and cosine makes this difference zero. Otherwise, we would need to subtract or add 3

## normalized loop variables

can substitute the filter expressions into His) and He(s).

Note type 1 filter is a type 2 with

$$T_2=0$$

} general passive  $\frac{1+j\omega\eta}{1+j\omega\eta}$  type 4 filter is a type 3 with  $T_2=0$  } general active  $\frac{1+j\omega\eta}{j\omega\eta}$

$$Pachive loop filter H(s) = \frac{K_0 K_d F(s)}{s + K_0 K_d F(s)} = \frac{K_0 K_d \frac{1 + s}{1 + s} \frac{\tau_2}{1 + s} \frac{1 + s}{1 + s} \frac{1 + s}{1 + s} \frac{\tau_2}{1 + s} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2} \frac{1 + k_0 K_d T_2}{1 + k_0 K_d T_2}$$

active loop filter:

$$H(s) = \frac{K_0 K_d \frac{1 + ST_2}{ST_1}}{ST_1} = \frac{K_0 K_d (1 + ST_2)}{K_0 K_d (1 + ST_2)}$$

$$= \frac{K_0 K_d (\frac{1 + ST_2}{ST_1})}{T_1}$$

$$= \frac{K_0 K_d (\frac{1 + ST_2}{T_1})}{T_1}$$

$$= \frac{K_0 K_d (\frac{1 + ST_2}{T_1})}{T_1}$$

note denominators of form

$$5^2 + 25 \omega_n 5 + \omega_n^2$$

where  $\omega_n = \text{natural frequency}$

$S = \text{damping factor}$

$$\omega_n = \sqrt{\frac{K_0 K_d}{T_1 + T_2}}$$

$$\zeta = \frac{1}{2} \sqrt{\frac{k_0 k_d}{\gamma_1 + \gamma_2}} \left( \gamma_2 + \frac{1}{k_0 k_d} \right)$$

## active loop

$$\omega_n = \sqrt{\frac{k_o K_d}{\tau_i}}$$

$$\zeta = \frac{T_z}{2} \sqrt{\frac{K_0 \, K_d}{T_1}}$$

Wn to NOT the center frequency of the VCO

this reduces the PLL transfer function to a simple from

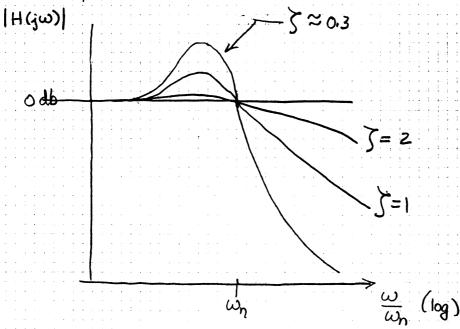

$$H(s) = \frac{s \omega_n \left(2 - \frac{\omega_n}{K_0 K_d}\right) + \omega_n^2}{s^2 + 2 s \omega_n s + \omega_n^2}$$

$$H(s) = \frac{2 \zeta \omega_n s + \omega_n^2}{s^2 + 2 \zeta \omega_n s + \omega_n^2}$$

if we calculate wo and 5 only unknown left is Kokd which is called to loop gain

If  $K_{o}K_{d} \gg \omega_{n}$ Kokd << wn

high gain loop (usually true) low gam loop

for a high-gam passive loop

$$H(s) \approx \frac{25\omega_n s + \omega_n^2}{s^2 + 25\omega_n s + \omega_n^2}$$

(the same as an active loop)

transient response

this graph is valid for every second order PLL a PLL is a low pass filter for phase signals  $\Theta_s(t)$  whose frequency spectrum is less than  $\omega_n$  i.e. the loop will track as long as the modulation frequency of  $\Theta_s(t)$  lies in  $[0, \omega_n)$

3 delermines the system overshoot

the description of the lock-in process must be done in the time domain. The linear model is invalid so the laplace transform cannot be used.

use

$$V_{e}(t) = k_{d} \sin \theta_{e}$$

$$F(j\omega) = \frac{1+j\omega \tau_{2}}{1+j\omega (\tau_{1}+\tau_{2})} = \frac{V_{d}(j\omega)}{V_{e}(j\omega)}$$

transform back to time domain

$$N_d(t) + \frac{dN_d}{dt} (T_1 + T_2) = N_e(t) + \frac{dN_e}{dt} T_2$$

The transfer function of the VCO is

$$\frac{\Theta_o(s)}{V_d(s)} = \frac{K_o}{s}$$

which after being inverse transformed is  $\theta(t) = K_0 \int V_d(t) dt$

$$\theta(t) = K_0 \int_0^\infty V_d(t) dt$$

If we combine all these equations we get the hon-linear differential equation for the phase error be

$$\frac{d^2 \Theta_e}{dt^2} + \frac{d \Theta_e}{dt} \frac{1 + k_0 k_d T_2 \cos \Theta_e}{T_1 + T_2} + \frac{k_0 k_d}{T_1 + T_2} \sin \Theta_e$$

$$= \frac{d^2 \Theta_s}{dt^2} + \frac{d \Theta_s}{dt} \frac{1}{T_1 + T_2}$$

which is a very hairy mon-linear differential equation usually Koka > 1 so that

$$\frac{d^2\theta e}{dt^2} + 25\omega_n \frac{d\theta_e \cos^2\theta}{dt} + \omega_n^2 \sin\theta_e = \frac{d^2\theta_s}{dt^2} + \frac{d\theta_s}{dt} \frac{\omega_n^2}{K_0 K_0}$$

nonlinearities

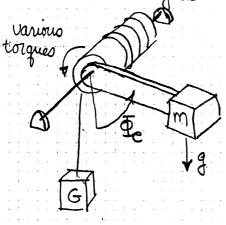

we can computer solve this equation or

we can solve analogous mechanical systems

JE - due to gravitation of mass M

JR - friction of cyclinder rotating

JA - torque generated by weight on arm.

phase error

$$\theta_e \iff \omega_n$$

angle of deflection De

$\sum_{i=1}^{n} a_i a_i = \sum_{i=1}^{n} a_i = \sum_{i=1$

3' due to viscous friction

reference phase disturbance

$$\theta_s + \theta_s \frac{\omega_n^2}{K_o K_d}$$

weight G

nate of change of frequency of fact.

frequency offset  $\theta(t) = \Delta w(t)$

$\Theta_{d}(t) = \Delta \omega$

So, by analogy, pulling different weights at different nates on 6

case I — G=0,  $P_e=0$  pendulum is vertically resting corresponds to PLL operating at center frequency up with zero of fact  $\Delta w=0$ Zero phase error  $\Theta e=0$  case II - reference signal of is changed slowly then of (+) can be neglected

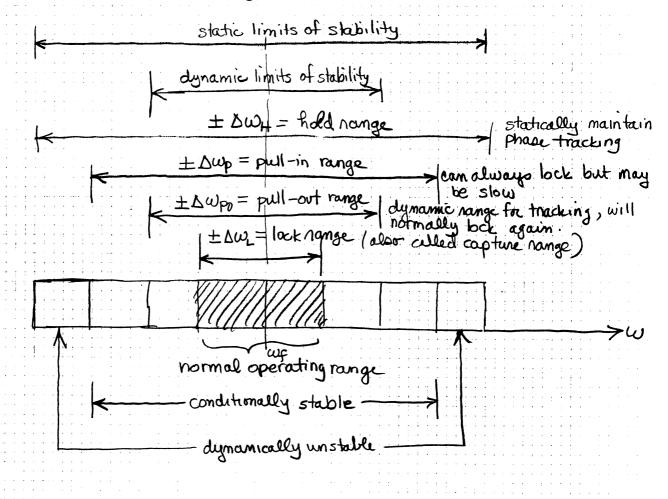

nochanically G slowly increases causing increased diffection of pendulum, if G causes the to increase beyond 90° the system will tip over 1.e. this is is static limit of stability the critical value of Dw is called to hold nange

case III

step change of  $\theta_s(t)$

$\theta_2 = \Delta \omega \, \mathcal{S}(t)$

we have a step Dw u(t)

plus an impulse Dw S(t)

corresponds to dropping a weight DG onto G

if the DG is small, we will simply have a smooth move (scullatory)

If the DG is moderate the swing can momentarily go beyond 90° but less than 180° and will oscillate back to a final  $\Phi_e$  < 90°

> there is a frequency step which causes the PLL to whock. This D frequency step is called the pull-out range. Pull-out nange is markedly smaller smaller than hold range.

Pull-out range is dynamic range of stability

case II - Dw increases linearly

too rapid an uncrease  $\Delta \omega$  will cause system to become unstable.

always need  $\Delta \dot{\omega} < \omega_n^2$

conditions for stability in phase tracking

- 1. angular frequency of Os(t) must be in the hold range

- 2 maximum frequency step Dw must be smaller than pull-out range

- 3. note of change of  $\theta_s(t)$  Dw must be less than  $\omega_n^2$

## The hold nange

$$\omega_s = \omega_t + \Delta \omega_H$$

want to calculate the DWH which will course a phase error of T.

$$\Theta_{z}(t) = \Delta \omega_{H} t$$

$$\Theta_{S}(S) = \frac{\Delta \omega}{S^2}$$

$$\frac{\Theta_{e}(s) = \Theta_{s}(s) H_{e}(s) = \left[\frac{\Delta W}{5^{2}}\right] \frac{K_{o} K_{d} F(s)}{s + K_{o} K_{d} F(s)}$$

$$\lim_{s \to \infty} \Theta_{e}(t) = \lim_{s \to \infty} s \Theta_{e}(s) = \lim_{s \to \infty} \left[\frac{\Delta W}{s}\right] \frac{s K_{o} K_{d} F(s)}{s + K_{o} K_{d} F(s)}$$

$$\lim_{s \to \infty} \frac{\Delta W}{s} \frac{s K_{o} K_{d} F(s)}{s + K_{o} K_{d} F(s)}$$

$$\lim_{t\to\infty} \sin \theta_e(t) = \frac{\Delta \omega}{K_0 K_d F(\emptyset)}$$

at limit of stability De= To and

$$\wedge$$

$\wedge \omega_{H} = \kappa_{o} \kappa_{d} F(\phi) = \begin{pmatrix} 1 & 1 \\ 1 & 1 \end{pmatrix}$

i.

$$\Delta \omega_{H} = K_{0}K_{d} F(0) = \begin{cases} \infty & \text{active loop} \\ K_{0}K_{0}F(0) \text{ passive loop} \end{cases}$$

limited to  $T_{2}$  for type 1 \$2

The foreign type 4.

limits of loop filter

the lock nange

$$\omega = \omega^2 + \nabla \omega$$

$$\frac{\omega_o}{\omega_f}$$

$$v_{e(t)} = K_{d} \left[ \sin(\Delta w)t + \sin(2\omega_{f} + \Delta w)t + \phi \right]$$

filtered out

$$N_d(t) \approx K_d |F(j\Delta\omega)| \sin(\Delta\omega t + \phi)$$

due to filter, not some  $\phi$

For locking want | Ko Va(t) | > Dw, i.e. the loop will quickly go thru the desired frequency.

$$\Delta \omega_{\perp} = K_0 \, K_d \, |F(j\Delta \omega)|$$

approximate  $|F(j\Delta \omega)| = \begin{cases} \frac{1}{\omega T_1} & \text{for type 1 $4$ } \text{filters} \\ \frac{T_2}{T_1 + T_2} & \text{for type 2} \end{cases}$

$$\frac{T_2}{T_1 + T_2} \text{ for type 3}$$

we can apply some approximations to get

DWL ≈ Wn for Type 1 and 4 filters ≈ 25 wn for type 2 and 3 filters

The pull in range

$\Delta \omega_{\rm p} \approx \frac{8}{\pi} \sqrt{\zeta \omega_{\rm n}} \, k_{\rm o} k_{\rm d} - \omega_{\rm n}^{2}$ for high gain loops this reduces to  $\Delta \omega_{\rm p} \approx \frac{8}{\pi} \sqrt{\zeta \omega_{\rm n}} \, k_{\rm o} \, k_{\rm d}$

## The pull out nange

from analog computer simulation  $\Delta \omega_{po} = 1.8 \omega_n (5+1)$

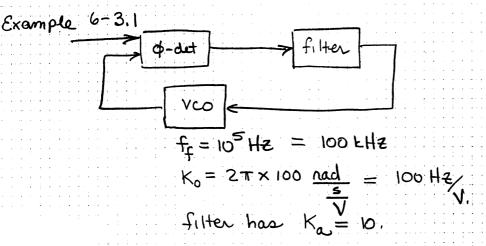

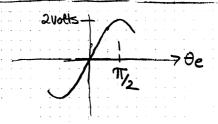

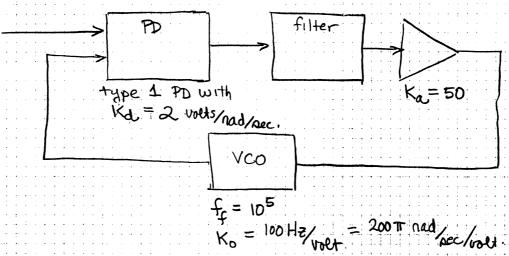

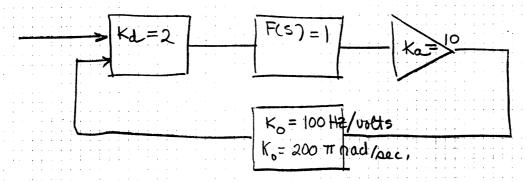

we a type 1 sinusoidal phase detector with  $V_{e,max} = 2 \text{ Volts } \Theta = \frac{\pi}{2}$ .

for a sinusoidal detector  $y_e^2 = K_d \sin \theta e^2$   $K_d = \frac{2}{1} = 2$

the open loop gain  $K_v = K_0 K_d F(\phi) = 200\pi \text{ nad}_{K_0}$ ,  $\frac{2V}{V}$ .

$= 4000 \pi$

hold-in range  $\Delta \omega_{\rm H} \approx \pm K_{\rm V} = \pm 4000 \,\pi$  rad/sec. or  $\Delta f_{\rm H} \approx \pm 2000 \,{\rm Hz}$

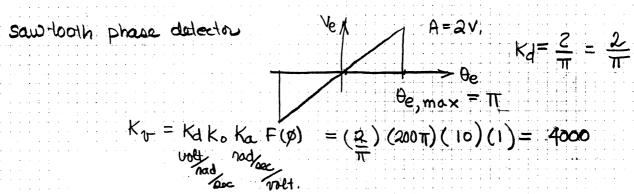

Example 6-3.2 Use a triangular PD (type 2) with

for a triangular PD  $K_d = \frac{2V}{7} = \frac{4}{7}$

open loop gain  $K_{v} = K_{o}K_{d}F(\phi) = \frac{4}{\pi} \cdot 200\pi \cdot 10$ = 8000

$\Delta \omega_{\text{H}} \approx \pm \text{Ky} \Theta_{\text{e,mox}} = \pm 8000 \, \text{T} = \pm 4000 \, \text{T}$

Overall, PLL design

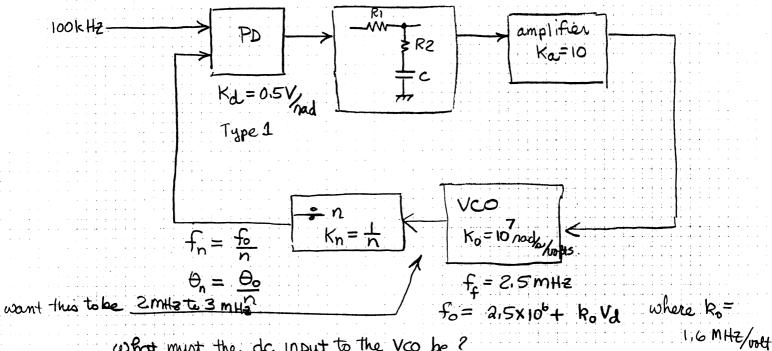

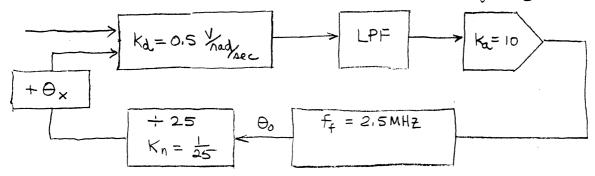

what must the do input to the voo be?

$$e^{n=20}$$

$V_d = \frac{f_0 - f_F}{k_0} = \frac{2.0 - 2.5}{1.6} = -0.3125 volt$

:.

$$V_e = \frac{V_d}{K_{av}} = \frac{-.3125}{10} = -.03125$$

volts.

$$\theta_e = \frac{V_e}{K_d} = \frac{-.03125}{.5} = -.0625$$

nadians

this is the phase shift needed to shift from the value at f, 1.e: Ve=0

$$\Delta \theta = n \Delta \theta_n = 20(-.0625) = -1.25$$

nadians

we now need to design only the filter  $K_{T} = (0.5)(1)(10)(10^{7})(\frac{1}{20}) = 2.5 \times 10^{6}$

5 is picked simply to be It remains to pick whand I, reasonably smooth -> pick >=0.8. Wn determines the modulation (max) for the loop. In this case it determines the frequency of the transient. Pick  $\omega_n = 10^4$  rad/sec. (Determines lock-up time  $\approx \frac{1}{\omega_n} = 0.1 \text{ mpec}$

$$\omega_{n} = \frac{K_{\infty}}{T_{1} + T_{2}}$$

$$S = \frac{\omega_{n}}{2} \left( T_{2} + K_{\infty} \right)$$

$$T_1 + T_2 = \frac{K_v}{\omega_n} - \frac{2.5 \times 10^6}{10^4} = .025 \text{ sec.}$$

$$T_2 = \frac{25}{\omega_n} - \frac{1}{K_v} = \frac{2(0.8)}{310^4} - \frac{1}{2.5 \times 10^6} = 1.596 \times 10^{-4}$$

$$R_2 = \frac{T_2}{c} = \frac{1,596 \times 10^{-4}}{.5 \times 10^{-6}} = 319 \Omega$$

$$R_1 = \frac{\tau_1}{c} = \frac{.025}{.5 \times 10^{-6}} \approx 50 \text{ k} \Omega.$$

6-3.1 Use the data of example 6-3.1

- (a) Find the hold-in range if the amplifier gain is increased to Ka=50,

- (b) Find the values of  $\theta e$ , Ve and Vd if the input-signal frequency is  $f_s = 100.5$  kHz.

(a)

$$K_{v} = K_{o}K_{d}F(\phi) = 200\pi \text{ rad/aec}$$

,  $2^{\text{rad}}50 = 20,000\pi$

$\Delta \omega_{H} = \pm K_{v} = \pm 20,000\pi$   $\Delta F_{H} = \pm \frac{20,000\pi}{2\pi} \pm 10\text{ kHz}$

(b)  $f_{s} = 100.5 \text{ kHz}$

$$V_{d} = \frac{f_{0} - f_{f}}{k_{0}} = \frac{100,500 - 100,000}{100} = \frac{500}{100} = 5 \text{ volts.}$$

$$V_{e} = \frac{V_{d}}{K_{a}F(\phi)} = \frac{5}{50} = 0.1$$

$$\theta_{e} = \frac{V_{e}}{K_{d}} = \frac{0.1}{2} = 0.05 \text{ volts.}$$

Note: usually linearize here because Ve is small i.e. instead of Ve = Kd sin  $\Theta e$  use the approximation  $Ve \approx Kd \Theta e$  as long as  $\Theta e$  is in radians

6-3.2 Use the PLL components of example b-3.1, but use a saw-tooth phase detector with A=2V. Show that the hold in range is the same as those found in examples b-3.1 and b-3.2.

$$\Delta \omega_{\text{H}} = \pm k_{\text{V}} \theta_{\text{e,max}} = \pm 4000 \cdot \pi = \pm 4000 \pi$$

6-3.3 Use the data of Example 6-3.2, except that the amplifier has Ka = 200 and it will saturate if its output exceeds 15 volls. What is the maximum phase error θe and steady state frequency deviation of that the loop can tolerate if the cumplifier voltage is the limiting factor?

$$V_{cl} = \pm 15 \text{ volts max}$$

$$f = f_f \pm V_{cl} R_0 = 100 \text{ kHz} \pm (15) \left(100 \frac{\text{Hz}}{\text{V}}\right)$$

$$\therefore \Delta f = 1500 \text{ Hz}.$$

maximum phase error:

$$V_{e,max} = V_{d} = 15 \text{ volts} = .0750$$

$$K_{a} = \frac{V_{e}}{\theta_{e}}$$

$$\theta_{e} = \frac{V_{e}}{K_{d}} = \frac{.0750}{4/\pi} = 0.0589 \text{ nadians}$$

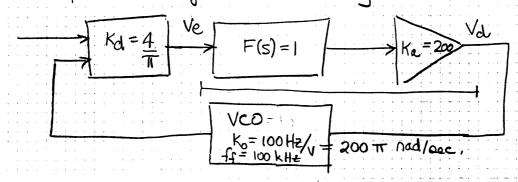

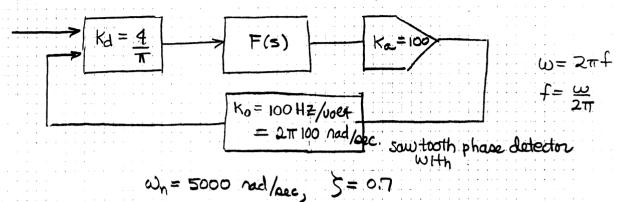

- 6-3.4 The PLL of example 6-3.2 is modified to use an amplifier with gain  $K_a = 100$ . The loop filter parameters are chosen to give  $w_n = 5000$  rad/sec. and  $\zeta = 0.7$

- (a) Find the hold-in range.

- (b) Find The approximate pull-in range.

(a)

$$K_{\nu} = K_{d} F(\phi) K_{\alpha} K_{o} = \frac{4}{\pi} \cdot 1 \cdot 100 \cdot 200 \pi = 80,000$$

$$\Delta\omega_{H} = \pm K_{T} \Omega_{e,max} = \pm 80,000 \left(\frac{\pi}{2}\right) = \pm 40,000 \pi$$

$$\Delta f_{H} = \frac{\Delta\omega_{H}}{2\pi} = \pm 20 \text{ kHz}$$

(b)

$$\Delta \omega_p \approx \pm \sqrt{2} \sqrt{2} \sum_n k_v - \omega_n^2$$

$$2(0.7)(5000)(80,000) = 560 \times 10^6$$

$\omega_n^2 = 25 \times 10^6$

$$\Delta \omega_{p} \approx \pm \sqrt{4 (560 - 25) \times 10^{6}} = \pm 46.26 \times 10^{3}$$

$$\Delta f_{p} = \frac{\Delta \omega_{p}}{2\pi} = \pm \frac{46.26}{2\pi} \times 10^{3} = \pm 7.4 \text{ kHz}.$$

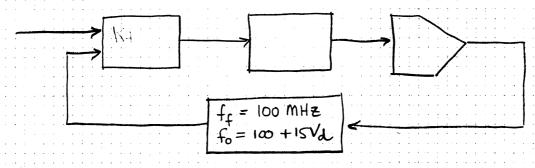

6-3.5 A phase-locked loop as shown in Fig. 6-2 is to be designed around the following elements: (1) a phase detector of the "triangular" type, Fig. 6-3b, with maximum output voltage of  $300\,\text{mV}$ , and (2) a vco with the characteristic of Fig. 6-5 with  $f_f$  = 100 mHz, and  $f_o$  = (100 + 15 Vd) mHz.

(a) The loop is to be designed to have a hold-in nange  $\pm \Delta f_H = \pm 5 \text{mHz}$ . Determine the values of  $K_V$ ,  $K_d$ ,  $K_o$  and  $K_a$

$$f_0 = f_f + k_0 Vd$$

$$2\pi f_0 = 2\pi f_f + 2\pi k_0 Vd$$

..

$$K_0 = 2\pi R_0 = 2\pi (15 \times 10^6) = 30\pi \times 10^6 = 94.25 \times 10^6$$

$$K_{v} = K_{o} K_{d} K_{a} F(\phi)$$

sawtooth

$$K_{V} = \pm \Delta \omega_{H} = \pm 2\pi 5 \times 10^{6} = 10 \times 10^{6}$$

$$K_{a} = \frac{K_{V}}{K_{0}K_{d}} = \frac{10 \times 10^{6}}{(30 \times 10^{6})(0.3)(1)} = \frac{10}{30(.3)}$$

$$= 1.11$$

(b) If the loop contains a low-pass filter like that of Fig 6-4a with R\_ = 1000 SZ, what is the value of C necessary to yield a 3-db bandwidth of 0.1 MHz for the filter?

$$\begin{array}{cccc}

& & & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& &$$

$$\frac{1}{2\pi (0.1 \times 10^{6})} = (1000)C$$

$$C = \frac{1}{2\pi (0.1) 10^{9}} = \frac{1}{628 \times 10^{6}} = 1.59 \text{ nF} = .0015 \text{ pf}$$

C) If fs = 99 mHz, find the values of Vd, Ve and De?

$$qq = f_0 = 100 + 15 \text{ Vd}$$

$$-1 = 15 \text{ Vd} \quad \text{i. } \text{Vd} = -\frac{1}{15} = -0.067 \text{ Volts.}$$

$$\text{Ve} = \frac{-.067 \text{ volts}}{1.11} = .060 \text{ volts.}$$

$$V_e = K_d \theta_e$$

$.060 = 0.3 \theta_e$

$$\Theta_{e} = \frac{.060 \, \pi}{.3} = 0.2 \pi = 0.628 \, \text{nadians}$$

Ve=0,  $\Delta\theta_0$  and  $\Delta\theta_0=0$ . Then a linear, voltage - controlled phase shifter is inserted between the frequency divider and the phase detector. If the phase shifter introduces a steady state phase shift  $+\theta_x$ , explain in detail what effect this will have on the phase angles  $\theta_e$ ,  $\theta_n$  (at the divider) output, and  $\theta_0$ . How will this affect the VCO frequency  $\theta_0$ ?

This corresponds to a phase step.  $\Theta_{x}$  u(t). It is immaterial whether the suift occurs in the signal or reference port of the phase detector. A second order PLL will always return the to zero (or its previous value) in response to a phase step. To prove this consider the laplace transform of the phase error transfer functions.

$$H_e(s) = \frac{\Theta_e(s)}{\Theta_o(s)} = \frac{s}{s + k_o k_d F(s)}$$

originally, we wrote (96(s) as the output from the oscillator. We can include the divider in the expression for  $k_0$ , i.e.  $k_0' = K_0 k_n = k_0/2$

Then,

$$\theta_e(s) = \frac{s}{s + k_0 k_n k_d F(s)} \cdot \frac{\theta_x}{s} = \frac{\theta_x}{s + k_0 k_n k_d F(s)}$$

Laplace transform of  $\theta_x$  u(t)

Using the final value theorem

$$\lim_{t\to\infty} \Theta_e(t) = \lim_{s\to 0} s\Theta_e(s) = \lim_{s\to 0} s \frac{\Theta_x}{s + \kappa_o \kappa_n \kappa_d F(s)} = 0.$$

This could also be seen from the mechanical model of + os

$\frac{d\Theta_s}{dt} = \Theta_x S(t)$ ,  $\frac{d^2\Theta_s}{dt^2} = \Theta_x S'(t)$ . The driving function is an impulse in response to which the phase error goes thru several oscillations and will return to zero if the loop did not unlock.

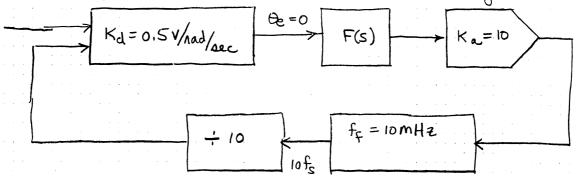

6-7.2 A PLL was a frequency dividen circuit (see Fig. 6-16) between the VCO and the phase detector so that the VCO operates at  $f_0=10f_8$ . The free-running frequency of the VCO is  $f_f=10\,\text{mHz}$ . If  $f_s=1\,\text{mHz}$  de at the phase detector is zero. Now suppose that  $f_s$  is changed by an amount of which results in  $\theta_e=0.1\,\text{radian}$ . What is the change in the phase angle  $\theta_0$  at the output of the VCO?

This problem is unlike 6-7.1 which applied a phase step. The input is now a frequency step  $\Delta f$  u(t). In terms of the mechanical model: frecall that  $\Theta_s(t)$  is the integral of  $W_s(t)$ , i.e.  $W_s(t) = W_0 + \Delta W$  u(t). Since  $\Theta_s(t) = \int_0^t \Delta W(t) dt$  we have  $\frac{d\Phi_s(t)}{dt} = \Delta W$  u(t),  $\frac{d^2\Phi_s(t)}{dt^2} = \Delta W S(t)$ . This means that the frequency step will generate a permanent mon-zero  $\Phi_s$ , with some oxillatory behavior as the loop error settles to a final value.

the constant De is necessary to put the loop at its offset frequency. Because of the dividers this corresponds to a phase shift of Inadian at the oscillator. Hence, the VCO has changed its phase angle by 57.3° (I radian)