# LAB 8 PRINCIPLES OF MOSFET AMPLIFICATION

# **Objective**

In this experiment you will study the input-output characteristics of an amplifier, using an n-channel MOS transistor (MOSFET). You will bias the transistor at an appropriate point for use as an amplifier, and will determine its voltage gain. You will also study the effect of the bias point on distortion.

### **BACKGROUND**

If you haven't done Lab 7, study its background section.

### A MOSFET-RESISTOR INVERTER

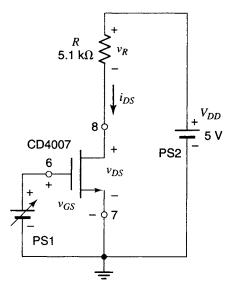

- 1. Hook up the circuit of Fig. 1, using connections as short as possible, and with the voltage of PS#1 set to zero for now. The chip that will be used in this experiment is the CD4007, the same chip used in the first half of Lab 7. Fig. 3 of that experiment shows the pin assignment for the transistor we will be using. The circuit of Fig. 1 will be used in the following steps to investigate the use of a MOSFET as an amplifier.

- 2. The gate-source voltage of the MOSFET,  $v_{GS}$ , is equal to the voltage of power supply PS#1. When this voltage is 0, the transistor current is virturally zero (this is the case for an enhancement-mode MOSFET, such as the one we will be using in this lab). If  $v_{GS}$  is gradually raised, initially the transistor current will remain at zero. When this voltage is raised sufficiently (to about the value of the threshold voltage of the transistor), the drainto-source current  $i_{DS}$  of the MOSFET will rise above zero. This will cause a voltage drop  $v_R = Ri_{DS}$  across the load resistor R. Using KVL you can see that the drain-source voltage  $v_{DS}$  will be equal to  $V_{DD}$   $v_R$ , and will thus be less than  $V_{DD}$ . As  $v_{GS}$  is increased,  $i_{DS}$  and thus  $v_R$  will also increase; therefore,  $v_{DS}$  will decrease. Eventually,  $v_{DS}$  can become so small that it limits further increases in  $i_{DS}$  and thus in  $V_R$ . Think what, qualitatively, a plot of  $v_{DS}$  versus  $v_{GS}$  will look like, without powering up the circuit.

- 3. Now take measurements and produce a plot of  $v_{DS}$  versus  $v_{GS}$ , with  $v_{GS}$  between 0 and 5 V Make sure that you take enough measurements to adequately reproduce the steep part of the plot.

Figure 1. MOSFET transistor

- 4. In the plot produced in the previous step, consider the point at which  $v_{DS} = 2.5 \text{ V}$ . What is the corresponding value of  $v_{GS}$  as obtained from this plot? Record this value.

- 5. Your plot should be steep around the point defined in the previous step. If  $v_{GS}$  varies around this point, the corresponding variation of  $v_{DS}$  should be larger. What is, approximately, the value of the slope  $(Dv_{DS})/(Dv_{GS})$  around this point?<sup>1</sup> Is it positive or negative? Why? The behavior you see is often said to be inverting. Why this name?

- 6. Set PS#1 so that  $v_{DS} = 2.5$  V We will use this as the bias value of  $v_{DS}$  (the use of this quantity will become clear shortly). Measure the corresponding value of  $v_{GS}$ ; this will be called the bias value of  $v_{GS}$ ; it should agree with the value you found in step 4. Record the bias values of  $v_{GS}$  and  $v_{DS}$  for further use.

- 7. Increase  $v_{GS}$  by a small amount  $Dv_{GS}$ , say 0.1 V, above its bias value. Record the corresponding change  $Dv_{DS}$  of vDS. From these results, calculate the small-signal voltage gain  $(Dv_{DS})/Dv_{GS}$ ). Does it agree with the value you found in step 5?

- 8. Repeat the above step, using instead a decrease of  $v_{GS}$  from its bias value (i.e.,  $Dv_{GS}$  should now be -0.1 V).

- 9. Move the knob of PS#1 back and forth slowly and continuously around the bias point, by about 0.1 V in either direction. Qualitatively observe the variation of  $v_{DS}$ .

- 10. What do you think  $v_{DS}$  would look like if  $Dv_{GS}$  were a sinusoidal voltage with an amplitude of 0.25 V?

<sup>&</sup>lt;sup>1</sup> DV denotes a small change in V.

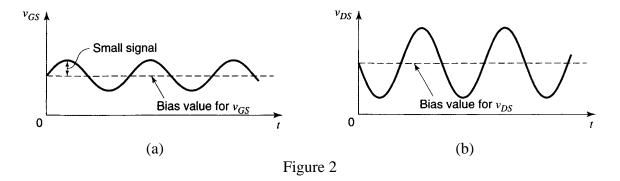

11. According to what you found so far, you can deduce that if you can superimpose a small signal to the gate-source bias voltage, so that it changes  $v_{GS}$  around the bias value, you will obtain an amplified version of this signal as a variation in  $v_{DS}$ . In other words, if  $v_{GS}$  looks like Fig. 2(a),  $V_{DS}$  will look like Fig. 2(b). The next step deals with a way to produce a voltage  $v_{GS}$  as in Fig. 2(a).

## ADDING A SIGNAL TO A DC BIAS VOLTAGE

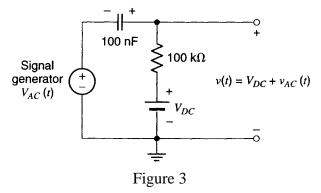

12. Consider the circuit of Fig. 3. It contains a DC source  $v_{DC}$  and an AC source  $v_{AC}(t)$ . The output voltage of the circuit is affected by both of these voltages. If the frequency of the signal is much higher than 1/(2pRC), the output of the circuit will almost be  $v(t) = v_{DC} + v_{AC}(t)$ , as indicated in the figure. To see this, consider the effect of each voltage source in the circuit by itself, as explained below.

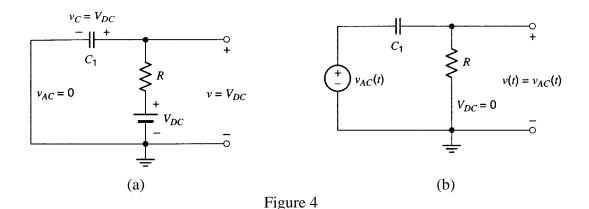

Assume, first, that  $v_{AC}(t) = 0$ ; this is equivalent to assuming that the signal generator is replaced by a short circuit, as shown in Fig. 4(a). Then the capacitor charges up to the DC voltage value, that is,  $v_C = v_{DC}$ . Using Kirchhoff's voltage law, we conclude that, in the steady state,  $v = v_{DC}$ , as indicated in the figure.

Assume now that the DC voltage in Fig. 3 is zero instead; this is equivalent to assuming that the DC source is replaced by a short, as shown in Fig. 4(b). The capacitor and resistor now form a high-pass filter with cutoff frequency 1/(2pRC). If the frequency of the signal is much higher than this, the signal will pass to the output; in other words,  $v(t) = v_{AC}(t)$ , as

Since the circuit is linear, superposition will apply: When both voltage sources in Fig. 3 are active, the output voltage will be the sum of the individual results in Figs. 4(a) and (b), that is,  $v(t) = v_{DC} + v_{AC}(t)$ , as indicated in Fig. 3. Thus, we have a circuit in which the AC voltage is coupled to the output through the capacitor (which is, for this reason, called a coupling capacitor) and is added to the DC voltage. At the same time, the capacitor blocks the DC voltage from reaching the AC source.

Hook up the circuit of Fig. 3. (CAUTION: It is unlikely that the 100 nF capacitor will have polarity indicated on it, but if it does, make sure to observe it, as shown in Fig. 3.) Use a DC voltage of 2 or 3 volts and a signal voltage with an amplitude of about 0.25 V and a frequency of 1 kHz. [Is this frequency much higher than 1/(2pRC) for this circuit?] Use the oscilloscope to observe the output signal. Make sure that you use the DC setting of the scope's input switch so that you can observe the total voltage and not just its AC variation. Do the following:

- (a) Use the amplitude control on the function generator to reduce the generator's output to zero, and verify that  $v = v_{DC}$ .

- (b) Use the variable voltage control on the power supply to reduce  $v_{DC}$  to zero, and raise the amplitude of the function generator output; verify that  $v(t) = v_{AC}(t)$ .

- (c) Finally, allow both  $v_{DC}$  and  $v_{AC}(t)$  to be nonzero, and verify that  $v(t) = v_{DC} + v_{AC}(t)$ .

### OBTAINING AC AMPLIFICATION WITH A MOSFET

indicated in the figure.

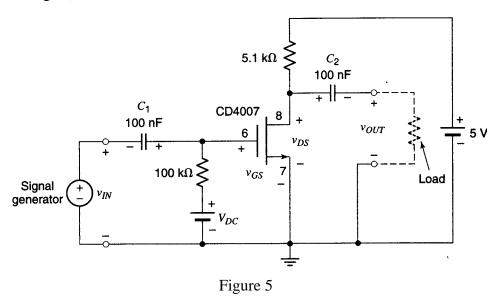

13. Remove PS #1 from the circuit of Fig. 1, and instead use the circuit of Fig. 3 to produce the voltage v<sub>GS</sub>, as shown in Fig. 5 (for now, set the signal amplitude to 0). The resistor shown connected across the output is meant to indicate any load the amplifier is supposed to drive; for our purposes, this load will be just a scope probe. The probe has a large input resistance (typically 1 MW) and can be connected there without disturbing the operation of the amplifier. Capacitor C<sub>2</sub> is a coupling capacitor, which allows the AC variation of v<sub>DS</sub>

to appear across the load but blocks the DC value of that voltage. Essentially,  $C_2$  forms a high-pass filter together with the load resistance. This filter passes the (high-frequency) AC variation of  $v_{DS}$  to the load but rejects the DC (i.e., zero-frequency) part of  $v_{DS}$  - (In the unlikely event that the capacitors indicate polarity on them, make sure to observe it, as shown in Fig. 5.)

- 14. Keep the input signal amplitude at zero. Adjust the value of  $v_{DC}$  until  $v_{GS}$  and  $v_{DS}$  assume the bias values determined in step 6.

- 15. Now try the circuit as an amplifier, using a 1 kHz input signal with an amplitude of 0.25 V. Use the scope to study the waveforms of v<sub>IN</sub>, v<sub>GS</sub>, v<sub>DS</sub>, and v<sub>OUT</sub>, as well as how these are related to one another. You can use both channels of the scope for this purpose. Use the center horizontal line as your zero reference (both traces should be positioned at that line when the input switches for both channels are at the ground position). A convenient vertical sensitivity to use for both channels, so that you can easily relate all results, is 2 V/division. To see the total voltage across gate-source and across drain-source, you need to use DC coupling for the scope inputs. If everything is working correctly, the variation of all these waveforms should be approximately sinusoidal; if it is not, reduce the signal amplitude somewhat, until the variation is approximately sinusoidal.

- 16. Sketch the above four waveforms. Make sure you understand the reason for their form. In particular, consider the waveforms for  $v_{GS}$  and  $v_{DS}$ ; are these two related as you would expect from the plot of step 3?

- 17. Does the relation between the input and output waveforms justify the name inverter for this circuit?

- 18. Verify that the input signal appears amplified at the output. What is the amplification factor?

- 19. Is the amplification factor approximately equal to those obtained in steps 5 and 7? It should be. Why?

- 20. Vary the input signal amplitude slowly, and observe  $v_{DS}$  with the scope. How large can the sinusoidal variation in  $v_{DS}$  be made before it is visibly distorted? Why do you think it gets distorted? Try to answer this question by referring to the plot you obtained in step 3.

- 21. As we have seen, the bias values of  $v_{GS}$  and  $v_{DS}$  are the DC values around which the signal variations occur. We will now try other bias values and will study their effect. Reduce the input signal amplitude to zero. Adjust the value of  $v_{DC}$  until the transistor is biased at  $v_{DS}$ =1 V Record the required value of  $v_{GS}$ . Then, increase the input amplitude somewhat, so that you can see a sinusoidal variation in  $v_{DS}$ . Determine the new amplification factor. Is it different from the one determined in step 18? Why? Answer this question by referring to the plot of step 3.

- 22. Increase the input signal amplitude, and determine how large the sinusoidal variation in  $v_{DS}$  can be made before significant distortion sets in. Is the result different from that in step 20? Why? To answer this question, again refer to the plot you obtained in step 3.

- 23. What bias value should one select for  $v_{DS}$  so that the maximum possible output signal amplitude, without significant distortion, is obtained from this circuit? Give the maximum output amplitude and the voltage gain for that bias point.

- 24. What is the range of signal frequencies that can pass through this amplifier? Take the lowest and highest usable frequencies to be the ones at which the voltage gain drops to 1/sqrt(2) = 0.707 of its value at 1 kHz. Audio amplifiers are often required to pass signals from 20 Hz to 20 kHz. Is this amplifier suitable for audio?

- 25. (Optional) If you have time, you can try to pass a music signal through your amplifier and feed the output to the power amplifier and speaker. The setup will be similar to that used in Experiment 5, except that here you would use a CD or cassette player as the signal source and your one-transistor amplifier rather than the op amp amplifier. You are on your own for this step.

NOTE: The circuits used in this experiment are kept simple to explain some basic principles. Although the method used above to bias the transistor is sometimes employed, this method turns out to be rather sensitive to temperature variations and device tolerances. You will learn how to design better biasing circuits in lectures and homework.