### Lab Reports

Reports should be in neat, concise form and turned in on time. The best reports will cover all vital information in detail without excessive verbiage on unnecessary details. Your report will typically follow the following format:

#### Title Page

Contains a typed one paragraph abstract and must be signed by you. The title page format you MUST use is on the following page.

#### Abstract (on the title page)

Explain in a few sentences what the program does. Describe how your program works and any special features of your program.

### Check Out (on the title page - ONLY IF REQUIRED)

Selected labs may require you to demonstrate how your lab assignment works. If you are required to demonstrate your program this line will be used by a Teaching Assistant to indicate that it worked properly.

#### Program Description (separate page - ONLY IF REQUIRED)

• main body of your program

Should include pseudo code or a flow chart (as appropriate, not all labs will need pseudo code or flow charts), input/output specifications, memory requirements, register and memory locations used, any algorithms used. Please cite any references you used for additional information. The program description should be concluded with a copy of your program listing; subroutine listings should be reserved for the description of each subroutine.

<u>any program subroutines</u> Should include a flow chart (if appropriate), input/output specifications, memory requirements, register and memory locations used, any algorithms used. Please cite any references you used for additional information.

#### Questions (separate page - ONLY IF REQUIRED)

Rather than a formal lab report each lab assignment will be accompanied by a series of questions which you must answer on a separate sheet. These questions will be graded and will form a major part of the lab grade.

#### Program Listing (separate page - REQUIRED)

You MUST include a copy of your program with every lab assignment you turn in. This should be an assembler listing which includes the symbol table for your program.

#### EEAP 282 TITLE PAGE

Names:

Typed

SIgnature

No laboratory will be graded unless it is signed. By signing this page you are indicating that this lab and that the work described in the lab report is your own. Any complaints about grading should be directed to Prof. Merat or the lab T.A.'s.

TITLE:

Abstract:

[ ] Checked by \_\_\_\_\_ \_

Basic computer operation and organization

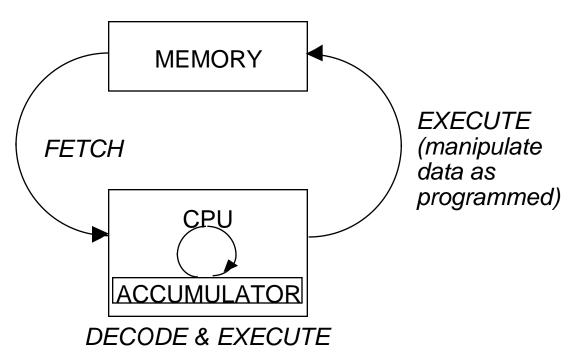

From an engineering viewpoint a computer manipulates coded data and responds to events occurring in the external world. This is called a storedprogram or von Neumann machine architecture.

- memory used to store both programs and data instructions (this is the core of the von Neumann architecture)

- program instructions are coded data which tells the computer to do something, i.e. adding two numbers together

- data is simply information to be used by the program, i.e. two numbers to be added together

We need something to decode the memory and determine what represents instructions and what represents data

central processing unit gets instructions and/or data from memory, decodes the instructions, and performs a sequence of programmed tasks

Nothing can occur simultaneously or instantaneously in a computer. Important operations are

- fetching instruction(s) from memory

- decoding the instruction(s)

- performing the indicated operations

This is the basic "fetch-execute" cycle

Problems with this diagram:

- what memory is being fetched?

- how does the computer tell program instructions from program data

- what happens when the program needs more than one piece of data?

Answers:

- put program instructions and data in separate areas of memory. These don't have to be well organized, but do need to be defined and can be intermixed. Usually program instructions are kept together.

- Internal pointers kept in special locations called registers in the CPU keep track of what data and program instructions are being referenced and/or fetched.

- The CPU has local storage in special locations called registers for temporary storage of data and/or instructions.

Keeping track of what instruction is being executed is so important that a special CPU register called the program counter is used to keep track of the address of the instruction to be executed.

### **Central Processing Unit**

| Control<br>Unit | Arithmetic<br>Logic Unit | Registers |

|-----------------|--------------------------|-----------|

|-----------------|--------------------------|-----------|

Control unit:

- decodes the program instructions

- program counter which contains the location of the next instruction to be executed

- status register which monitors the execution of instructions and keeps track of overflows, carries, borrows, etc.

RISC reduced instruction set machine

• executes a simple set of instructions very fast

CISC complex instruction set (such as the 68000)

has a powerful set of instructions which allows many complex operations to be represented as a single instruction

Arithmetic Logic Unit

- carries out the instructions decoded by the control unit

- Older microprocessors had special registers called accumulators which had to be used for math calculations. Modern microprocessors such as the 68000 have general-purpose registers and do not have accumulators.

Memory

- RÓM read-only memory non-volatile all bits can be read, no bits can be changed

- RAM random access memory (not really a good name since almost all memory has random access capability)

volatile all bits can be read and/or written

User concern with memory

- large computer usually don't even think about memory organization

- mini computer sequence of RAM, how much RAM, etc.

- micro computer memory constraints on RAM, ROM. Very limited address space.

Computer memory is always organized in a fixed manner:

- 16k x 1 bit

- 4k x 1 bit

- 8k x 8 bits typical of small microcomputers

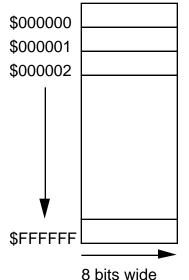

Vertical grid organization of memory:

This diagram represents  $FFFFF = 2^{24}$  bytes of memory

• Any particular processor will have an x-bit address capacity:

| 64k  | 6502, Z-80, 8085, etc. |

|------|------------------------|

| 640k | 8088                   |

| 16MB | 68000                  |

| lots | 80386, 68030           |

- memory addresses do not need to be contiguous

- ROM and RAM can be intermixed

memory does not have to start at \$000000 or end at \$0FFFFF

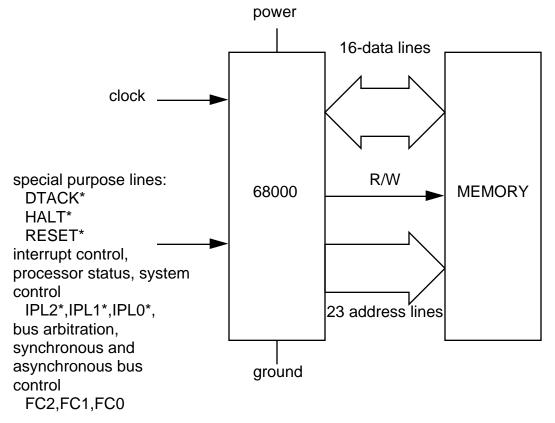

### 68000 architecture:

### 68000's internal register organization:

### data registers:

|    | 31 | 16 15 | 87 | 7 0 |

|----|----|-------|----|-----|

| D0 |    |       |    |     |

| D1 |    |       |    |     |

| D2 |    |       |    |     |

| D3 |    |       |    |     |

| D4 |    |       |    |     |

| D5 |    |       |    |     |

| D6 |    |       |    |     |

| D7 |    |       |    |     |

### address registers:

| 31 16 | 15 0  |

|-------|-------|

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       | 31 16 |

### stack pointers:

| A7 | user stack pointer   |

|----|----------------------|

|    | system stack pointer |

### program counter:

| 23 |                 | 0 |

|----|-----------------|---|

| PC | program counter |   |

### status register:

| 15     | 87   | 7         | 0 |

|--------|------|-----------|---|

| system | byte | user byte |   |

### SOFTWARE ARCHITECTURE:

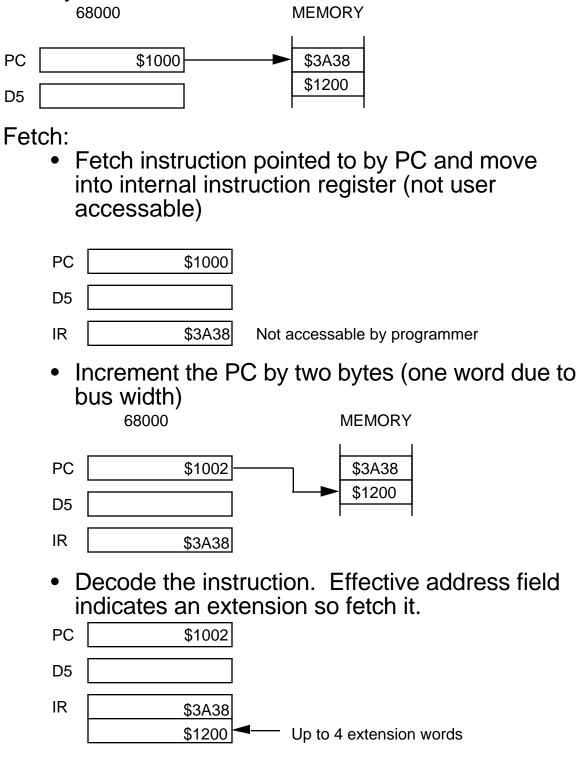

### Basic fetch-execute cycle:

loop: fetch\_instruction execute\_instruction goto loop.

### Program counter:

Because the computer must keep track of instruction locations it uses the program counter to keep track of the address of the next instruction to be executed:

loop: instruction\_register = fetch\_instruction(pc\_address)

decode\_instruction(instruction\_register)

execute\_instruction(instruction\_register)

goto loop.

Instruction\_register is an internal (to the processor) memory location (register) used to store coded data (instructions).

### Instructions are coded data in the following format:

op\_code source(s) destination next\_instruction

The exact way this information is represented is different for every microcomputer. Present microcomputers typically code instructions in several somewhat simplified formats op code source1 source2/destination

or

op\_code source/destination

where source, source1 and source2 identify where any needed data is to be obtained and the result (if any) is to be placed in a destination which is also the second source of needed data. For example, x:=x+y is represented in the first format as ADD Y X

### Add processing to decode instructions:

Our original fetch-execute cycle has now become more complex:

loop: instruction\_register = fetch\_instruction(pc\_address)

decode\_instruction(instruction\_register)

while extension\_flag set do

fetch additional information

update pc\_address

end while.

execute\_instruction(instruction\_register)

update pc\_address.

update status register.

goto loop.

Instructions which require more than one computer word to describe can be indicated by extension\_flag and fetched until the instruction is complete.

The exact manner in which memory locations are represented is known as addressing and can directly effect the program execution speed of the computer.

### Basic computer operation and organization

Use hex to represent memory locations as seen by the microcomputer. Memory can be organized as:

• bytes

| address | memory |

|---------|--------|

| \$0     | byte 0 |

| \$1     | byte 1 |

| \$2     | byte 2 |

| \$3     | byte 3 |

| \$4     | byte 4 |

| \$5     | byte 5 |

• words

| address | memory |        |        |

|---------|--------|--------|--------|

| \$0     | byte 0 | byte 1 | word 0 |

| \$2     | byte 2 | byte 3 | word 1 |

| \$4     | byte 4 | byte 5 | word 2 |

| \$6     | byte 6 | byte 7 | word 3 |

| \$8     |        |        | word 4 |

| \$A     |        |        | word 5 |

long words

addres

| ress |        | memory |        |        |

|------|--------|--------|--------|--------|

| \$0  | byte 0 | byte 1 | byte 2 | byte 3 |

| \$4  | byte 4 | byte 5 | byte 6 | byte 7 |

| \$8  | byte 8 | byte 9 | byte A | byte B |

| \$C  | byte C | byte D | byte E | byte F |

### Machine code (stored program execution)

z := x + yhigh level C or Pascal representationwhere x,y,and z will represent words in memory

Data:

| Ζ | is at memory address \$1204 |

|---|-----------------------------|

|---|-----------------------------|

- x is at memory address \$1200

- y is at memory address \$1202

address memory

contents

|        |      |      |      |      | 0011101110 |

|--------|------|------|------|------|------------|

| \$1200 | 0001 | 0010 | 0011 | 0100 | \$1234     |

| \$1202 | 0100 | 0011 | 0010 | 0001 | \$4321     |

| \$1204 | 0000 | 0000 | 0000 | 0000 | \$0000     |

For some reason we decided to use words (16 bits) for all operations.

Instructions:

| address | memory |    | meaning                   |

|---------|--------|----|---------------------------|

| \$1000  | 3A     | 38 | move a word from \$1200   |

|         | 12     | 00 | to D5                     |

| \$1004  | DA     | 78 | add the word at \$1202 to |

|         | 12     | 02 | the contents of D5        |

| \$1008  | 31     | C5 | move the contents of D5   |

|         | 12     | 04 | to \$1204                 |

| \$100C  | 4E     | 40 | stop                      |

Coding of an instruction. This is an opcode word as defined by Motorola for the 68000. See The MC68000 Programmer's reference Manual.

| 15 14                                                                            | 13 12                                              | 11 10 9                                                                                 | 8    | 7    | 6    | 5     | 4     | 3    | 2                              | 1    | 0                           |

|----------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|-------|------|--------------------------------|------|-----------------------------|

| op<br>code                                                                       | size                                               | destir                                                                                  | nati | on   |      |       |       | SO   | urce                           | Э    |                             |

|                                                                                  |                                                    | register                                                                                | r    | noc  | le   | r     | noc   | de   | re                             | egis | ter                         |

| first four<br>bits are<br>the op<br>code,<br>indicates<br>a move in<br>this case | size code<br>01=byte<br>11=word<br>10=long<br>word | Dn = data<br>register<br>Abs.w =<br>absolute<br>word<br>Abs.L=abso<br>lute long<br>word | hov  | v to | mani | ipula | ite d | ata: | reg<br>Abs<br>abs<br>wo<br>Abs | -    | r<br>=<br>te<br>abso<br>ong |

In this case the \$3A38 instruction at \$1000 would be interpreted as a MOVE instruction. (see p.4-116 of the Programmer's Reference Manual, current edition)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 1 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 1  | 1  | 1  | 0  | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

|  | first four<br>bits are<br>the op<br>code for a<br>move | word<br>length | D5 data<br>register | put data<br>into<br>register | get data<br>from<br>memory<br>address<br>(word<br>length)<br>which<br>follows<br><u>EXTENSION</u><br>WORD | word length<br>address |

|--|--------------------------------------------------------|----------------|---------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|

|--|--------------------------------------------------------|----------------|---------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|

Disassembly is the interpretation of coded instructions The instructions we just used are interpreted as:

### \$3A38 1200

| 0011 1010 00<br>0011 101 000 |         | rewrite as binary<br>regroup into the<br>appropriate fields: op code,<br>destination, and source                          |

|------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| op code                      | 00XX    | indicates a MOVE, move data from source to destination                                                                    |

| size                         | 11      | indicates word length                                                                                                     |

| destination                  | 101 000 | 0                                                                                                                         |

| mode                         | 000     | indicates to a data register                                                                                              |

| register                     | 101     | indicates to register D5                                                                                                  |

| source                       | 111 000 | 5                                                                                                                         |

| mode                         | 111     | indicates one of several                                                                                                  |

| register                     | 000     | possible modes: absolute and<br>PC relative<br>indicates that Abs.W is being<br>used requiring a 16-bit<br>extension word |

|                              |         | a word length move of<br>of \$1200 to D5                                                                                  |

### \$DA78 1202

1101 1010 0111 1000 rewrite as binary The form of this instruction is different from that of the MOVE. The 1101 op code indicates that this is an ADD.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

1

0

1

register

Op-mode

Effective Address

mode

register

0

0

0

0

0

0

|                       |        |       |      |                                                    | mode | register |

|-----------------------|--------|-------|------|----------------------------------------------------|------|----------|

| op c<br>indic<br>this | ates a | n ADD | ) in | specifies one<br>of the eight<br>data<br>registers |      |          |

|                       |        |       |      |                                                    |      |          |

| 1101 101 00 | )1 111 000 | appropriate fields: op c<br>register, op-mode, and             | ode,       |

|-------------|------------|----------------------------------------------------------------|------------|

|             |            | effective address                                              |            |

| op code     | 1101       | indicates an ADD, add bina                                     | ry         |

| register    | 101        | indicates register D5                                          |            |

| op-mode     | 001        | indicates word length add of                                   | f the      |

|             |            | form ( <dn>) + (<ea>) <d< td=""><td>)n&gt;</td></d<></ea></dn> | )n>        |

|             |            |                                                                | - <b>f</b> |

parentheses are used to indicate the contents of

### effective address

|          | 000          |                               |

|----------|--------------|-------------------------------|

| mode     | 111          | indicates absolute or PC      |

|          |              | relative addressing           |

| register | 000          | indicates that Abs.W is being |

| register | 000          | used                          |

|          |              | u360                          |

| instruct | ion is a     | a word length add of the      |

|          |              | •                             |

| contant  | te of C      | 1202 to the contents of       |

| COLICELI | $301$ $\psi$ |                               |

| DE with  | tha ra       | ault haing put into DE        |

|          |              | sult being put into D5        |

|          |              | 01                            |

### <u>\$31C5 1204</u>

|      | 1 0001 11<br>1 000 111  |                       | rewrite as binary<br>regroup into the<br>appropriate fields: op code,<br>destination, and source |

|------|-------------------------|-----------------------|--------------------------------------------------------------------------------------------------|

| ор с | code                    | 00XX                  | indicates a MOVE, move data<br>from source to destination                                        |

| size |                         | 11                    | indicates word length                                                                            |

| dest | tination                | 000 111               | 5                                                                                                |

|      | mode                    | 111                   | indicates one of several possible modes: absolute and PC relative                                |

|      | register                | 000                   | indicates that Abs.W is being used                                                               |

| SOUI | rce<br>mode<br>register | 000 101<br>000<br>101 | indicates from a data register indicates from register D5                                        |

instruction is a word length move of the contents of D5 to \$1204

# Your textbook (p.54-55) lists several common instructions:

| MOVE | copy 16-bit word specified by the source |

|------|------------------------------------------|

|      | into the location specified by the       |

|      | destination operand                      |

|      |                                          |

| 303C <number></number>                     | MOVE.W | #N,D0                   |

|--------------------------------------------|--------|-------------------------|

| 33FC <number>,<address></address></number> | MOVE.W | #N, <address></address> |

| 3039 <address></address>                   | MOVE.W | <address>,D0</address>  |

| 33C0 <address></address>                   | MOVE.W | D0, <address></address> |

| 3300 <auliess></auliess>                   |        | D0, <auuress></auuress> |

ADD

adds the 16-bit word specified by the source and the 16-bit contents of the destination. The result is stored in the destination:

(<source>) + (<destination>) <destination>

| 0640 <number></number>                     |

|--------------------------------------------|

| 0679 <number>,<address></address></number> |

| D079 <address></address>                   |

| D179 <address></address>                   |

ADDI.W ADDI.W ADD.W ADD.W

#N,D0 #N,<address> <address>,D0 D0,<address>

### SUB

subtracts the 16-bit word specified by the source from the 16-bit contents of the destination. The result is stored in the destination:

(<destination>) - (<source>) <destination>

| 0440 <number></number>                     | SUBI.W | #N,D0                   |

|--------------------------------------------|--------|-------------------------|

| 0479 <number>,<address></address></number> | SUBI.W | #N, <address></address> |

| 9079 <address></address>                   | SUB.W  | <address>,D0</address>  |

| 9179 <address></address>                   | SUB.W  | D0, <address></address> |

Example: Chapter 3, problem 25

| 00010A | 303C | 000A           |

|--------|------|----------------|

| 00010E | 33C0 | 0000 020A      |

| 000114 | 0679 | 00C3 0000 020C |

| 00011C | 9079 | 0000 020C      |

| 000122 | 0679 | 0AF3 0000 020A |

| 00012A | 0640 | 00F8           |

|        |      |                |

| 00020A | 0036 |

|--------|------|

| 00020C | 03FA |

All numbers are in hex. Each line indicates an individual instruction.

Initially, (D0) = 0000 003B, (\$020A)=\$0036, (\$020C)=\$03FA

The disassembled program:

| MOVE.W<br>MOVE.W | #10,D0<br>D0,\$020A | put \$A into D0<br>put the contents of D0<br>(\$A) into address \$20A                                             |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------|

| ADDI.W           | #\$C3,\$020C        | add \$C3 to the contents of \$020C (\$3FA) and put                                                                |

| SUB.W            | \$20C,D0            | the result into \$20C<br>subtract what's in \$20C<br>from the contents of D0<br>(\$A) and put the result in<br>D0 |

| ADDI.W           | #\$0AF3,\$020A      | add \$0AF3 to the                                                                                                 |

| ADDI.W           | #\$F8,D0            | contents of \$20A<br>add \$F8 to the contents<br>of D0                                                            |

The detailed disassembly:

| <u>303C 000A</u><br>0011 0000 00<br>0011 000 000 |                       | rewrite as binary<br>regroup                                                                                                 |

|--------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|

| op code<br>size<br>destination                   | 00XX<br>11<br>000 000 | indicates a MOVE<br>indicates word length MOVE                                                                               |

| mode<br>register<br>source                       | 000                   | indicates data register<br>register D0                                                                                       |

| mode<br>register                                 | 111<br>100            | any of several modes<br>indicates immediate mode,<br>designated as Imm, i.e. a<br>constant contained in an<br>extension word |

| MOVE.V                                           | V #10,D0              |                                                                                                                              |

| <u>33C0 0000 0</u>                               | <u>20A</u>            |                                                                                                                              |

| 0011 0011 1<br>0011 001 11                       |                       | rewrite as binary regroup                                                                                                    |

| op code<br>size<br>destination                   | 00XX<br>11<br>001 111 | indicates a MOVE<br>indicates word length MOVE                                                                               |

| mode<br>register                                 | 111<br>001            | indicates any of several modes<br>indicates Abs.L, a long word<br>address requiring two extension<br>words                   |

| source<br>mode<br>register                       | 000 000<br>000<br>000 | indicates a data register<br>register D0                                                                                     |

MOVE.W D0, \$0000 020A

#### 0679 00C3 0000 020C 0000 0110 0111 1001 rewrite as binary 0000 0110 01 111 001 regroup 0000 0110 indicates an ADDI op code word operation, i.e. one 16-01 size bit extension word effective address 111 mode indicates Abs.L, requires a 32register 001 bit longword address, i.e. two 16-bit extension words ADDI.W #\$C3, \$0000 020C 9079 0000 020C

| 1001 0000 01<br>1001 000 001   |                    | rewrite as binary regroup                                                                     |

|--------------------------------|--------------------|-----------------------------------------------------------------------------------------------|

| op code<br>register<br>op-mode | 1001<br>000<br>001 | indicates a SUB<br>indicates D0<br>word operation, i.e.<br>( <dn>)-(<ea>) <dn></dn></ea></dn> |

| effective add                  | ress               |                                                                                               |

| mode                           | 111                |                                                                                               |

| register                       | 001                | indicates Abs.L, requires a 3                                                                 |

indicates Abs.L, requires a 32bit longword address, i.e. two 16-bit extension words

SUB.W \$0000 020C, D0

#### 0679 0AF3 0000 020A 0000 0110 0111 1001 rewrite as binary 0000 0110 01 111 001 regroup 0000 0110 op code indicates an ADDI word operation, i.e. one 16size 01 bit extension word effective address mode 111 001 indicates Abs.L, requires a 32register bit longword address, i.e. two 16-bit extension words

ADDI.W #\$0AF3, \$0000 020A

0640 00F8

| 0000 0110 02000 0110 02000 0110 02000 |                 | rewrite as binary<br>regroup                                                                            |

|---------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------|

| op code<br>size                       | 0000 0110<br>01 | <ul> <li>indicates an ADDI</li> <li>word operation, i.e. one 16-</li> <li>bit extension word</li> </ul> |

| effective add<br>mode<br>register     | 000 i           | indicates data register<br>indicates D0                                                                 |

ADDI.W #\$F8, D0

#### The final program is then If (D0)=\$3B, (\$20A) = \$36, (\$20C) = \$3FA MOVE.W #10.D0 (D0)=\$A D0,\$020A MOVE.W (\$20A)=\$000A #\$C3,\$020C ADDI.W (\$020C) = (\$020C) + \$C3= \$3FA + \$C3 = \$4BD (D0) = (D0) - (\$20C) =\$20C,D0 SUB.W \$A-\$4BD = \$ FB4D (\$20A) = (\$20A) + \$0AF3ADDI.W #\$0AF3,\$020A = \$A + \$0AF3 = \$0AFD (D0) = (D0) + F8 =ADDI.W #\$F8,D0 \$FB4D + \$F8 = \$FC45

Math: 000A

0000 0000 0000 1010

| 04BD       | 0000 | 0100 | 1011 | 1101 |

|------------|------|------|------|------|

| complement | 1111 | 1011 | 0100 | 0010 |

| add 1      | 1111 | 1011 | 0100 | 0011 |

| 000A  | 0000 0000 0000 1010 |

|-------|---------------------|

| -04BD | 1111 1011 0100 0011 |

| FB4D  | 1111 1011 0100 1101 |

| +00F8 | 0000 0000 1111 1000 |

| FC45  | 1111 1100 0100 0101 |

### ADD

Add Binary

### ADD

**Operation:** (Source)+(Destination) Destination

Assembler ADD <ea>,Dn

Syntax ADD Dn,<ea>

Attributes: Size=(Byte,Word,Long)

**Description:** Add the source operand to the destination operand, and store the result in the destination location. The size of the operation may be specified to be byte, word, or long. The mode of the instruction indicates which operand is the source and which is the destination as well as the operand size.

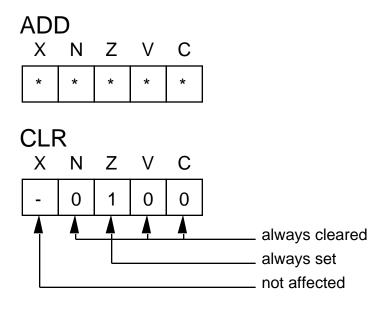

#### **Condition Codes:**

| Х | Ν | Ζ | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

- N Set if the result is negative. Cleared otherwise.

- Z Set if the result is zero. Cleared otherwise.

- V Set if an overflow is generated. Cleared otherwise.

- C Set if a carry is generated. Cleared otherwise.

- X Set the same as the carry bit.

#### Instruction Format:

| 15 | 14 | 13 | 12 | 11 | 10    | 9  | 8  | 7    | 6  | 5        | 4    | 3     | 2   | 1    | 0 |

|----|----|----|----|----|-------|----|----|------|----|----------|------|-------|-----|------|---|

| 1  | 1  | 0  | 1  | R  | egist | er | Op | o-Mo | de |          | Effe | ctive | Add | ress | ; |

|    |    |    |    |    | -     |    |    |      |    | Mode Reg |      | egist | er  |      |   |

#### **Instruction Fields:**

Register field — Specifies any of the eight data registers.

Op-Mode field —

| Byte | Word | Long | Operation                |           |

|------|------|------|--------------------------|-----------|

| 000  | 001  | 010  | ( <dn>)+(<ea>)</ea></dn> | <dn></dn> |

| 100  | 101  | 110  | ( <ea>)+(<dn>)</dn></ea> | <ea></ea> |

Effective Address field — Determines addressing mode:

a. If the location specified is a source operand, then all addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|-----------------|------|-----------------|

| Dn              | 000  | register number | d(An,Xi)        | 110  | register number |

| An*             | 001  | register number | Abs.W           | 111  | 000             |

| (An)            | 010  | register number | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number | d(PC)           | 111  | 010             |

| -(An)           | 100  | register number | d(PC,Xi)        | 111  | 011             |

| d(An)           | 101  | register number | Imm             | 111  | 100             |

\* Word and Long only.

b. If the location specified is a destination operand, then only alterable memory addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|-----------------|------|-----------------|

| Dn              |      | —               | d(An,Xi)        | 110  | register number |

| An              |      | —               | Abs.W           | 111  | 000             |

| (An)            | 010  | register number | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number | d(PC)           | _    | —               |

| -(An)           | 100  | register number | d(PC,Xi)        | _    | —               |

| d(An)           | 101  | register number | Imm             | _    | _               |

**Notes:** 1. If the destination is a data register, then it cannot be specified by using the destination <ea> mode, but must use the destination Dn mode instead.

2. ADDA is used when the destination is an address register. ADDI and ADDQ are used when the source is immediate data. Most assemblers automatically make this decision.

Move Data From Source to Destination

MOVE

**Operation:** (Source) Destination

- Assembler MOVE <ea>,<ea> Syntax

- Attributes: Size=(Byte,Word,Long)

Description: Move the content of the source to the destination location. The data is examined as it is moved, and the condition codes set accordingly. The size of the operation may be specified to be byte, word or long.

#### **Condition Codes:**

| Х | Ν | Ζ | V | С |

|---|---|---|---|---|

| — | * | * | 0 | 0 |

- Set if the result is negative. Cleared otherwise. Ν

- Z V Set if the result is zero. Cleared otherwise.

- Always cleared.

- С Always cleared.

- Х Not affected.

#### **Instruction Format:**

|           | 15 | 14 | 13 | 12 | 11 | 10     | 9  | 8     | 7    | 6 | 5 | 4    | 3 | 2    | 1     | 0  |

|-----------|----|----|----|----|----|--------|----|-------|------|---|---|------|---|------|-------|----|

|           | 0  | 0  | Si | ze |    |        |    | natio |      |   |   |      |   | irce |       |    |

|           |    |    |    |    | R  | egiste | er |       | Mode | Э |   | Mode | е | Re   | egist | er |

| . Fielder |    |    |    |    |    |        |    |       |      |   |   |      |   |      |       |    |

#### **Instruction Fields:**

Size field — Specifies the size of the operand to be moved.

- 01 byte operation. \_

- \_ 11 word operation.

- \_ 10 long operation.

Destination Effective Address field - Specifies the destination location. Only data alterable addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|-----------------|------|-----------------|

| Dn              | 000  | register number | d(An,Xi)        | 110  | register number |

| An              |      | —               | Abs.W           | 111  | 000             |

| (An)            | 010  | register number | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number | d(PC)           | _    | —               |

| -(An)           | 100  | register number | d(PC,Xi)        | _    | —               |

| d(An)           | 101  | register number | Imm             | _    | —               |

Source Effective Address field - Specifies the source operand. All addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|-----------------|------|-----------------|

| Dn              | 000  | register number | d(An,Xi)        | 110  | register number |

| An*             | 001  | register number | Abs.W           | 111  | 000             |

| (An)            | 010  | register number | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number | d(PC)           | 111  | 010             |

| -(An)           | 100  | register number | d(PC,Xi)        | 111  | 011             |

| d(An)           | 101  | register number | Imm             | 111  | 100             |

\* For byte size operation, address register direct is not allowed.

Notes: 1. MOVEA is used when the destination is an address register. Most assemblers automatically make this distinction.

2. MOVEQ can also be used for certain operations on data registers.

### **ADDI**

Add Immediate

###

**Operation:** Immediate Data + (Destination) Destination

Assembler Syntax

ADD #<data>,<ea>

Attributes: Size=(Byte,Word,Long)

**Description:** Add the immediate data to the destination operand, and store the result in the destination location. The size of the operation may be specified to be byte, word, or long. The size of the immediate data matches the operation size.

#### **Condition Codes:**

| Х | Ν | Ζ | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

- Set if the result is negative. Cleared otherwise. Ν

- Z V Set if the result is zero. Cleared otherwise.

- Set if an overflow is generated. Cleared otherwise.

- Set if a carry is generated. Cleared otherwise. С

- Х Set the same as the carry bit.

#### **Instruction Format:**

| 15                                           | 14                                     | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5                 | 4 | 3  | 2 | 1 | 0 |

|----------------------------------------------|----------------------------------------|----|----|----|----|---|---|----|----|-------------------|---|----|---|---|---|

| 0                                            | 0                                      | 0  | 0  | 0  | 1  | 1 | 0 | Si | ze | Effective Address |   |    |   |   | ; |

|                                              |                                        |    |    |    |    |   |   |    |    | Mode Regist       |   | er |   |   |   |

|                                              | Word Data (16 bits) Byte Data (8 bits) |    |    |    |    |   |   |    |    |                   |   |    |   |   |   |

| Long Data (32 bits, including previous word) |                                        |    |    |    |    |   |   |    |    |                   |   |    |   |   |   |

**Instruction Fields:**

Size field — Specifies the size of the operation.

- byte operation. 00 —

- \_\_\_ word operation. 01

- 10 \_ long operation.

Effective Address field - Specifies the destination operand. Only data alterable addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        |  | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|--|-----------------|------|-----------------|

| Dn              | 000  | register number |  | d(An,Xi)        | 110  | register number |

| An              |      | —               |  | Abs.W           | 111  | 000             |

| (An)            | 010  | register number |  | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number |  | d(PC)           | _    | —               |

| -(An)           | 100  | register number |  | d(PC,Xi)        | —    | —               |

| d(An)           | 101  | register number |  | Imm             | —    |                 |

Immediate field — (Data immediately following the instruction):

If size=00, then the data is the low order byte of the immediate word.

If size=01, then the data is the entire immediate word.

If size=10, then the data is the next two immediate words.

### SUB

Subtract Binary

### SUB

**Operation:** (Destination)-(Source) Destination

Assembler SUB <ea>,Dn

Syntax SUB Dn,<ea>

Attributes: Size=(Byte,Word,Long)

**Description:** Subtract the source operand from the destination operand, and store the result in the destination. The size of the operation may be specified to be byte, word, or long. The mode of the instruction indicates which operand is the source and which is the destination as well as the operand size.

#### **Condition Codes:**

| Х | Ν | Ζ | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

- N Set if the result is negative. Cleared otherwise.

- Z Set if the result is zero. Cleared otherwise.

- V Set if an overflow is generated. Cleared otherwise.

- C Set if a carry is generated. Cleared otherwise.

- X Set the same as the carry bit.

#### Instruction Format:

|   | 15 | 14 | 13 | 12 | 11 | 10    | 9  | 8  | 7       | 6 | 5    | 4                 | 3 | 2     | 1  | 0 |

|---|----|----|----|----|----|-------|----|----|---------|---|------|-------------------|---|-------|----|---|

| ſ | 1  | 0  | 0  | 1  | R  | egist | er | Op | Op-Mode |   |      | Effective Address |   |       |    | ; |

|   |    |    |    |    |    | -     |    |    |         |   | Mode |                   | R | egist | er |   |

#### **Instruction Fields:**

Register field — Specifies any of the eight data registers.

Op-Mode field —

| Byte | Word | Long | Operation                |           |

|------|------|------|--------------------------|-----------|

| 000  | 001  | 010  | ( <dn>)-(<ea>)</ea></dn> | <dn></dn> |

| 100  | 101  | 110  | ( <ea>)-(<dn>)</dn></ea> | <ea></ea> |

Effective Address field — Determines addressing mode:

a. If the location specified is a source operand, then all addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        |  | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|--|-----------------|------|-----------------|

| Dn              | 000  | register number |  | d(An,Xi)        | 110  | register number |

| An*             | 001  | register number |  | Abs.W           | 111  | 000             |

| (An)            | 010  | register number |  | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number |  | d(PC)           | 111  | 010             |

| -(An)           | 100  | register number |  | d(PC,Xi)        | 111  | 011             |

| d(An)           | 101  | register number |  | Imm             | 111  | 100             |

\* For byte size operation, address register direct is not allowed

b. If the location specified is a destination operand, then only alterable memory addressing modes are allowed as shown:

| Addressing Mode | Mode | Register        |  | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|--|-----------------|------|-----------------|

| Dn              | —    | —               |  | d(An,Xi)        | 110  | register number |

| An              | —    | _               |  | Abs.W           | 111  | 000             |

| (An)            | 010  | register number |  | Abs.L           | 111  | 001             |

| (An)+           | 011  | register number |  | d(PC)           | —    | _               |

| -(An)           | 100  | register number |  | d(PC,Xi)        | _    | _               |

| d(An)           | 101  | register number |  | Imm             | _    |                 |

**Notes:** 1. If the destination is a data register, then it cannot be specified by using the destination <ea> mode, but must use the destination Dn mode instead.

2. SUBA is used when the destination is an address register. SUBI and SUBQ are used when the source is immediate data. Most assemblers automatically make this distinction.

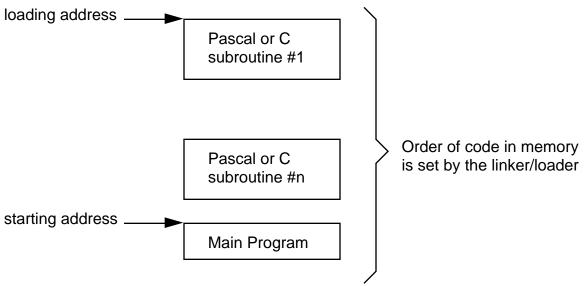

### Running Programs (See Section 3.5.2 of your text)

starting address set by the assembler or the linker. loading address set by the linker.

The Program Counter (PC) MUST be set before you can run a program.

You can do this in the debugger in several ways:

- 1. Memory Register @PČ=1000h <You cannot use \$1000 in the debugger>

- 2. Program Step From 1000h Program Step

You can also automatically set the PC in the assembler <label> <your code begins here> rest of your program end <label> where <label> is any name you want. It will be used to set the initial PC value.

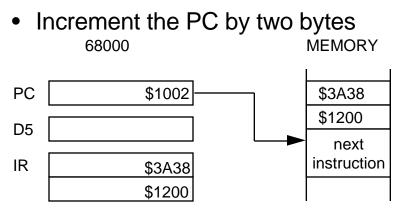

## Fetch and execute for a simple example: Initially:

- Execute the instruction uses address in extension word to fetch (\$1200)

- Repeat

You can look up how long it takes instructions to execute:

MOVE.W \$1200,D5 This has one extension word, addressing modes are xxx.W and Dn From Table D.2 in Programmer's Reference Manual, Appendix D

| Source  | Destination | Clock periods<br>(read/writes) |

|---------|-------------|--------------------------------|

| (xxx).W | Dn          | 16(4/0)                        |

ADD.W \$1202,D5 From Table D.4 in Programmer's Reference Manual, Appendix D

| Instruction                                   | Size          | op <ea>,Dn</ea> |  |  |  |  |  |  |  |  |

|-----------------------------------------------|---------------|-----------------|--|--|--|--|--|--|--|--|

| ADD                                           | word          | 4(1/0)+         |  |  |  |  |  |  |  |  |

| Now use Table                                 | D.1 to comput | e the cycles    |  |  |  |  |  |  |  |  |

| required to compute the effective address and |               |                 |  |  |  |  |  |  |  |  |

| execute any feto                              | ches          |                 |  |  |  |  |  |  |  |  |

| (xxx).W                                       | Absolute      | word=8[2/0]     |  |  |  |  |  |  |  |  |

|                                               | short         |                 |  |  |  |  |  |  |  |  |

| MOVE.W D5,\$                                  | 61204         |                 |  |  |  |  |  |  |  |  |

| Now use Table                                 | D.2 to comput | e the cycles    |  |  |  |  |  |  |  |  |

| required to compute the effective address and |               |                 |  |  |  |  |  |  |  |  |

| execute any fetches                           |               |                 |  |  |  |  |  |  |  |  |

| Dn                                            | (xxx).W       | 12(2/1)         |  |  |  |  |  |  |  |  |

### More detailed example:

### Assume PC=\$100

| instruction | address | machine code        | mnemonics         |

|-------------|---------|---------------------|-------------------|

| 1           | 000100  | 3039 0000 2000      | MOVE.W \$2000,D0  |

| 2           | 000106  | 0679 0012 0000 2004 | ADDI.W #18,\$2004 |

### program execution

| program excedution |                                                                       |

|--------------------|-----------------------------------------------------------------------|

| read cycle         | put (PC) on address bus,<br>(CPU)<br>put 3039 on data bus<br>(memory) |

|                    | decode 3039, increment<br>PC to 102                                   |

| read cycle         | put 102 on address bus<br>read 0000 from memory,<br>PC 104            |

| read cycle         | put 104 on address bus<br>read 2000 from memory,<br>PC 106            |

| read cycle         | put 2000 on address bus<br>read (\$2000)<br>pc stays at 106           |

This is instruction:

MOVE.W source xxx.L

source xxx.L destination Dn

From Table D.2, it takes 16 clock cycles (4 reads/0 writes) to execute.

# YOU WANT FAST INSTRUCTIONS WHENEVER POSSIBLE, i.e. NO extension words.

Example: MOVEQ does not use an extension word.

| 15      | 14 | 13 | 12 | 11            | 10 | 9 | 8                         | 7 | 6 | 5 | 4  | 3    | 2 | 1 | 0 |

|---------|----|----|----|---------------|----|---|---------------------------|---|---|---|----|------|---|---|---|

| 0       | 1  | 1  | 1  |               |    |   | 0                         |   |   |   | SO | urce | 9 |   |   |

| op code |    |    |    | = da<br>ister |    |   | 8 bit constant128 to +127 |   |   |   |    |      |   |   |   |

### Section 5.1 The Condition Code Register (CCR)

| 16-bit<br>15 | statu    | s regis | ster<br>37                                                                      |   |   | 0 |   |  |  |  |

|--------------|----------|---------|---------------------------------------------------------------------------------|---|---|---|---|--|--|--|

| Syste        | ems info | rmation | CCR                                                                             |   |   |   |   |  |  |  |

| 7            | 6        | 5       | 4                                                                               | 3 | 2 | 1 | 0 |  |  |  |

|              |          |         | Х                                                                               | Ν | Ζ | V | C |  |  |  |

| bits         |          |         | func                                                                            |   |   |   |   |  |  |  |

| 7,6,5<br>4   |          |         | not used<br><u>extend bit</u><br>retains carry bit for multi-word<br>arithmetic |   |   |   |   |  |  |  |

| 3            |          |         | negative<br>set to 1 if instruction result is<br>negative, set to 0 if positive |   |   |   |   |  |  |  |

| 2            |          |         | zero<br>set to 1 if result is 0                                                 |   |   |   |   |  |  |  |

| 1            |          |         | overflow<br>set if signmed overflow occurs                                      |   |   |   |   |  |  |  |

| 0            |          |         | carry/borrow                                                                    |   |   |   |   |  |  |  |

NOTE:

| MOVE<br>MOVE<br>MOVE | <ea>,CCR<br/><ea>,SR<br/>CCR,</ea></ea> | only effects CCR<br>effects entire SR<br>only effects CCR |  |  |  |  |

|----------------------|-----------------------------------------|-----------------------------------------------------------|--|--|--|--|

| MOVE                 | SR.                                     | (upper byte is set to all<br>0's)<br>entire SR            |  |  |  |  |

|                      | JN,                                     |                                                           |  |  |  |  |

These are word length instructions.

| The System Part of the SR |                      |    |    |                                                                                                           |    |   |   |   |  |  |  |

|---------------------------|----------------------|----|----|-----------------------------------------------------------------------------------------------------------|----|---|---|---|--|--|--|

| 15                        | 14                   | 13 | 12 | 11                                                                                                        | 10 | 9 | 8 | _ |  |  |  |

| Τ                         |                      | S  |    |                                                                                                           | 2  | 1 | 0 |   |  |  |  |

|                           | <u>its</u><br>1,12,1 | 1  |    | function                                                                                                  |    |   |   |   |  |  |  |

|                           | <u>,9,10</u>         | 14 |    | not used<br><u>interrupt mask</u><br>a priority scheme to determine<br>who has control of the<br>computer |    |   |   |   |  |  |  |

| 1                         | 3                    |    |    | supervisor<br>set to 0 if user, set to 1 if<br>supervisor                                                 |    |   |   |   |  |  |  |

| 1                         | 5                    |    |    | trace<br>set to 1 if program is to be<br>single stepped                                                   |    |   |   |   |  |  |  |

Any unused (reserved) bit is always set to zero! You can always read the entire SR, but you can only modify the system byte of the SR in supervisor mode.

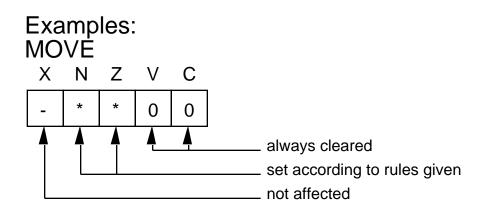

### Even a MOVE instruction effects the status register

| over | flov | N |          |   | V | С | )                                                       |                                     |

|------|------|---|----------|---|---|---|---------------------------------------------------------|-------------------------------------|

| carr | У    |   |          |   | С | С | )                                                       |                                     |

| nega | ativ | e |          |   | Ν | * |                                                         | Depends on<br>number being<br>moved |

| zerc | )    |   |          |   | Z | * |                                                         | Depends on<br>number being<br>moved |

| exte | nd   |   |          |   | Х | - |                                                         | Not changed                         |

| MO   | VЕ   |   |          |   |   |   |                                                         |                                     |

| Х    | Ν    | Ζ | V        | С |   |   |                                                         |                                     |

| -    | *    | * | 0        | 0 |   |   |                                                         |                                     |

|      |      |   | <b>A</b> |   |   |   | always cleared<br>set according to rule<br>not affected | es given                            |

Examples: MOVE.W LENGTH,D1 if (LENGTH)=0 then (Z) 1

> MOVE.B #\$FF,D1 (Z) 0, (N) 1

How an instruction effects the SR is shown in the Programmer's Reference Manual and on the Programmer's Reference Card Examples of status flags (all word length)

Consider an add instruction of the form ADD.W D0,D3

| <b>15</b> 10 | addition of | 0000 0000 0000 11112                  | Overflow |

|--------------|-------------|---------------------------------------|----------|

|              | two         | <u>0000 0000 0000 1111</u> 2          |          |

| <b>30</b> 10 | positive    | $\overline{0000\ 0000\ 0001\ 1110}_2$ | Carry    |

|              | signed      |                                       | C=0      |

|              | numbers     |                                       |          |

|              |             |                                       |          |

|                          |          | 0000 0000 0111 1110 <sub>2</sub> |     |

|--------------------------|----------|----------------------------------|-----|

| 3 <u>10</u>              | two      | 0000 0000 0000 00112             | V=1 |

| <b>129</b> <sub>10</sub> | positive | 1000 0000 0000 0001 <sub>2</sub> |     |

|                          | signed   | (this is -127 <sub>10</sub> )    | C=0 |

|                          | numbers  |                                  |     |

The result  $129_{10}$  is out of range for a signed 16-bit number. As a result, the sign of the result does not match that of the operands and signed overflow occurrs.

| <u>-3<sub>10</sub></u><br>-5 <sub>10</sub> | two<br>negative<br>integers<br>with no<br>overflow | $\begin{array}{c} 11111 \ 11111 \ 11110_2 \\ \underline{11111} \ 11111 \ 11111 \ 1101_2 \\ 11111 \ 11111 \ 11111 \ 1101_2 \\ \\ \hline \\ \text{with a carry} \end{array}$ | V=0<br>Carry<br>C=1 |

|--------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                            |                                                    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                      |                     |

The signs match so no signed overflow occurred.

| -127 <sub>10</sub><br>-5 <u>10</u> | addition of two                          | 1000 0000 0000 0001 <sub>2</sub><br>1111 1111 1111 1011 <sub>2</sub> |  |

|------------------------------------|------------------------------------------|----------------------------------------------------------------------|--|

|                                    | negative<br>integers<br>with<br>overflow | 0111 1111 1111 1011 <sub>2</sub> with a carry                        |  |

The result -13210 is out of range for a signed 16-bit so the signs don't match and signed overflow occurred. In addition a carry occurred.

| <b>128</b> 10 | addition of                      | 1000 0000 0000 0000 <sub>2</sub> |              |

|---------------|----------------------------------|----------------------------------|--------------|

| 15 <u>10</u>  | two                              | 0000 0000 0000 11112             | V=0          |

| 14310         | positive<br>unsigned<br>integers | 1000 0000 0000 1111 <sub>2</sub> | Carry<br>C=0 |

| <b>128</b> 10            | addition of | 1000 0000 0000 0000 <sub>2</sub>        | Overflow |

|--------------------------|-------------|-----------------------------------------|----------|

| <u>143<sub>10</sub></u>  |             | <u>1000 0000 0000 1111</u> <sup>2</sup> |          |

| <b>271</b> <sub>10</sub> | positive    | 0000 0000 0000 1111 <sub>2</sub>        | Carry    |

|                          | unsigned    | with a carry                            | C=1      |

|                          | integers    |                                         |          |

The same analysis can be applied to subtraction:

SUB.W D0,\$1200 where (D0)=\$0F13 and (\$1200)=\$01C8

| <b>456</b> 10   | subtraction of | \$ 01 C8   | Overflow V=0 |

|-----------------|----------------|------------|--------------|

| -3859 <u>10</u> | two signed     | + \$ F0 ED | Carry C=0    |

| -340310         | numbers        | \$F2 B5    | •            |

Note that since the result is negative this would be sign extended if to long word if the instruction length were .L

### Simple assembly language example:

### PROGRAM 4.1 of text

| field#1                   | field#2<br>ORG      | field#3<br>\$1000          | ;start program at this memory location                                                                                      |

|---------------------------|---------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| * CODED                   | INSTRUCTIONS        | _                          |                                                                                                                             |

| MAIN:                     | MOVE                | DATA,D5                    | ;get first number, use<br>symbol for it                                                                                     |

|                           | ADD<br>MOVE<br>TRAP | NEXT,D5<br>D5,ANSWER<br>#0 | add NEXT to D5                                                                                                              |

| * DATA                    | ORG<br>DECLARATIONS | \$1200                     |                                                                                                                             |

| DATA:<br>NEXT:<br>ANSWER: | DC<br>DC<br>DS      | \$1235<br>\$4321<br>1      | <pre>;put \$1235 into location ;put \$4321 into location ;reserves one word of memory ; could also have used DC.W \$0</pre> |

|                           | END                 | MAIN                       | ;stop assembler                                                                                                             |

#### NOTES:

- 1. Program in text uses HEXIN and HEXOUT. These do not work in our debugger. You will be introduced to their equivalent in Lab #3.

- 2. Use of symbols in programs is highly recommended to make them more readable.

- 3. Symbol table contains a symbol field, type field, and a value field.

- 4. Use of colons (:) following labels is optional if the label's name begins in column 1.

- 5. Use of the semi-colon to begin a comment is also optional.

You can write programs in machine code but that is:

- tedious

- slow

- prone to errors

So, use programs to make process more efficient

source program

### assembler

linker/loader

(uses mnemonics for machine code)

translates mnemonics into machine code; calculates addresses, etc. references any system calls; loads program into memory

Cross-assemblying is when you assemble on another machine, say an 80286, using a program to generate 68000 machine code.

Down-line loading is when you transfer object code between machines. When you transfer your code to the in-circuit emulator you are downloading.

| Example of m | nnemonic in | struction: |       |

|--------------|-------------|------------|-------|

| MOVE         | .W          | D0,        | D3    |

| op code      | word length | from D0    | to D3 |

| mnemonic     |             |            |       |

| for a move   |             |            |       |

It would take a great deal of effort to calculate addresses all the time so a good assembler allows you to assign names to program locations and constants.

For example, MOVE.W D5, DATA instead of MOVE.W D5,\$1200 Section 4.2 of textbook describes program organization

Labels are <u>implied</u> if they precede a valid instruction code and begin in column 1. Labels are <u>defined</u> if they are followed by a colon.

implied: LOOP MOVE.W D5,DATA defined: LOOP: MOVE.W D5,DATA

Comments are implied if they follow a valid instruction on a line. In some assemblers they must be preceded by a semi-colon (;) or asterisk (\*). Comments are defined if they begin with a "\*" in column 1.

Assembler directives tell the assembler to perform a support task such as beginning the program at a certain memory location.

- ORG tells the assembler where that section of the program is to go in memory

- END end of entire program (including data). Put the starting label after the END for automatic loading of the starting PC.

- DC puts a set of data into meory (define constant) DS reserves specified memory locations

Many assembler directives and instructions can operate on bytes, words or long words. What is to be acted on is indicated by the suffix:

- .B byte length operations

- .W word length operations (almost always assumed)

- .L long word operations

- \$ indicates a hex number, decimal is assumed otherwise (Does not work in debugger.)

- h follows number in debugger to indicate hex. Hex constants in debugger must begin with a number.

- # preceded an immediate constant

- D0-D7 data registers

- A0-A7 address registers

Some assemblers will print out a symbol table which will list all variables, including labels, and their values.

The EQU directive (F&T, Section 6.3.2)

Directly puts something in the symbol table. Such a symbol is NOT a label, but a constant! Use EQU to define often-used constants.

| LENGTH | EQU | \$8     |

|--------|-----|---------|

| MASK   | EQU | \$000F  |

| DEVICE | EQU | \$3FF01 |

can also use the format LABEL EQU \* which enters the current value of the PC as its value

SET is the same as EQU but you can re-define the value of the variable later in your program.

- XREF tells the assembler/linker that the following symbol(s) are defined in another program module (file)

- XDEF tells the assembler/linker that the following symbol(s) are defined in this program module for use (reference) by another program module. Described on p.204-205 of F&T.

| DATA<br>PROGRAM                    | EQU<br>EQU                                                              | \$6000<br>\$4000                                                 |                                                                                 |

|------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|

| ORG<br>* TABLE O<br>FTABLE<br>test | DATA<br>F FACTOR:<br>DC<br>DC<br>DC<br>DC<br>DC<br>DC<br>DC<br>DC<br>DC | IALS<br>1<br>2<br>6<br>24<br>120<br>720<br>5040                  | 0!=11!=12!=23!=64!=245!=1206!=7207!=5040                                        |

| VALUE                              | DS.B<br>DS.B                                                            | 1<br>1                                                           | input to factorial function<br>align on word boundary                           |

| RESULT                             | DS.W                                                                    | 1                                                                | result of factorial                                                             |

|                                    |                                                                         |                                                                  |                                                                                 |

| ORG<br>main<br>*                   | PROGRAM<br>NOP<br>NOP                                                   |                                                                  | PUT TABLE BASE ADDRESS IN A0                                                    |

|                                    | MOVEA.W<br>MOVEA.W<br>MOVE.W                                            | #FTABLE,A0<br>FTABLE,A1<br>#FTABLE,A2<br>#FTABLE,D0<br>FTABLE,D1 |                                                                                 |

|                                    | MOVE.W                                                                  | test(A0),D3                                                      | test displacement                                                               |

|                                    | MOVE.W                                                                  | #5,VALUE                                                         | inputto fact is 5                                                               |

| fact                               | MOVE.W<br>ADD.W<br>LEA<br>MOVE.W<br>MOVE.W                              | VALUE,D5<br>D5,D5<br>FTABLE,A3<br>0(A3,D5),D6<br>D6,RESULT       | get input<br>double for word offset<br>get base address<br>get result<br>output |

END main

How to run your program:

# as68k Example1

Assumes a file with the full name Example1.s is present. Produces an output Example1.o

This is a two-pass assembler. The first pass reads the entire program, computes all instruction addresses, and assigns addresses to labels. The second pass converts all instructions into machine code using the label addresses.

## Id68k -o Example1 Example1

The first file name following the -o is the output file which will automatically be named Example1.x; the second file name is the input which is assumed to be Example1.o

# db68k Example1

You must set the PC in the debugger to run your program. You can do this in the debugger in several ways:

- 1. Memory Register @PC=1000h <You cannot use \$1000 in the debugger>

- 2. Program Step From 1000h Program Step

You can also automatically set the PC in the assembler <label> <your code begins here> rest of your program

end <label>

where <label> is any name you want. It will be used to set the initial PC value.

### SOME USEFUL DEBUGGER COMMANDS ARE:

| Debugger Quit Yes <return></return>                | Quits the debugger.                                                                                                                                                      |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Window Active Assembly Registers <return></return> | Removes the journal window and shows the Status Register.                                                                                                                |

| Program Step From 1000h <return></return>          | Resets the code<br>window to \$1000 and<br>executes the<br>instruction at \$1000.<br>Note that only one<br>instruction is executed.                                      |

| Program Step <return></return>                     | Executes the<br>instruction currently<br>highlighted. This<br>command following the<br>initial Program Step<br>From 1000h would<br>execute the instruction<br>at \$1006. |

| Memory Register @PC=1000h <return></return>        | Sets the current value<br>of the PC to \$1000, i.e.<br>this is the next<br>instruction to be<br>executed.                                                                |

| Memory Register @A3=1000h <return></return>        | Sets the current<br>contents of A3 to<br>\$1000. Can be used<br>for all registers<br>including SR.                                                                       |

| Expression Monitor Value @A1                       | Continuously displays the value of A1 in the monitor window.                                                                                                             |

NOTE: The @ indicates a reserved symbol such as the name of a data or address register, the PC or the SR.

# COMMENTS ON MC68000 INSTRUCTIONS IN LAB#2

\* These instructions operate on data registers #\$FFFE.D0 MOVE.W ;you will get different results if you use .L instructions #1,D0 ADD.W ADD.W #1.D0 #\$FFFE.D0 ADD.W ADD.W #2,D0 \* These instructions operate on address registers LEA \$2000,A0 MOVE #\$2000,A1 this is not an allowed instruction. assembler will automatically convert to MOVEA MOVE D0,(A0) address register: indirect

If you look at the MOVE instruction, An is not allowed. You must use a MOVEA which can only have an address register as a destination. The instruction MOVEA <ea>,A1

is the only form of the MOVE that can put data into an address register. The size of the operator can be .W or .L Word size operands are sign extended to 32 bits before any operations are done.

The LEA instruction is subtly different than a MOVEA it computes <effective address> and puts that into An. Only a long form of the instruction is allowed.

| MOVEA<br>LEA | converts addresses into constants<br>generates position independent<br>code using PC relative address<br>modes; better for position |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| MOVE D0,(A0) | independent code<br>moves contents of D0 into address<br>location stored in A0                                                      |