# IV. Final Report

[1] Karl Doering, Nadim Addus, Heath Deuel, Steven Gyford, Oscar Servin, Michael Wilson, entitled - Wireless Communication Systems Block Analysis and Design. The Technical Faculty Advisor for this project was the author, in collaboration with Mr. Dave Devries, Mr. Bob Kelly, and Mr. Daniel Kong of the Maxim Corporation.

We have selected this item, because of our personal involvement in its creation. We hope that this report would be of both interest and help to our future students.

More importantly, we have included this project to emphasize that a multi-team project must be assembled coherently. As stated in the opening remarks of Section II of this part, senior design projects should be the result of a marriage between engineering programs and industry, a prospect that is fruitful for all parties involved. But that is not an easy task to arrange, since people in industry are under different sets of constraints from their counterparts in academia. In some instances, it may require decades of pursuing and working relationships with industry to build enough trust to let our students in their facility, nevertheless it can be done and should be explored.

Senior design projects may provide golden opportunities for a qualified faculty member to develop and operate a successful research enterprise continually, provided that projects are selected coherently and with an eye to the future. Thus, those who shy away from contributing to this activity are missing a remarkable chance to enhance their research productivity while helping undergraduate students. This instructor has enjoyed the experience of working with many of these young students specially when they come up with their "awesome" results.

Just as any good story, there is a time that one must say farewell and leave the reader. We close by saying that it has been truly an enjoyable year to work on this project. Best wishes to all you young people and so long until we meet again.

# Final Report of Senior Design Project Winter / Spring 2001 Professor Mansour Eslami

# The University of California at Riverside Department of Electrical Engineering

# Wireless Communication Systems Block Analysis and Design

# Prepared by: Karl Doering, Nadim Addus, Heath Deuel, Steven Gyford, Oscar Servin, Michael Wilson

# Technical Advisors:

Dr. Mansour Eslami, Faculty Advisor

Mr. Dave Devries, Manager, Strategic Applications Engineering at Maxim Corporation

Mr. Bob Kelly, Senior Corporate Applications Engineer at Maxim Corporation

Mr. Daniel Kong, Strategic Customer Applications Engineer at Maxim Corporation

This project is supported in part by a contract with Maxim Corporation.

Submitted on June 7, 2001 at 5:00 PM

Executive Summary — We analyze and improve upon a Wideband Code-Division Multiple Access transceiver, dividing the task at the block level into three portions: receive, transmit, and frequency synthesis. Each portion is attacked by a team of two EE senior design students at UC Riverside, working with an industry engineer from Maxim Integrated Products. After performing preliminary research and analysis to become familiar with the reference architecture and design issues involved, each team works on a particular aspect of the design as described herein.

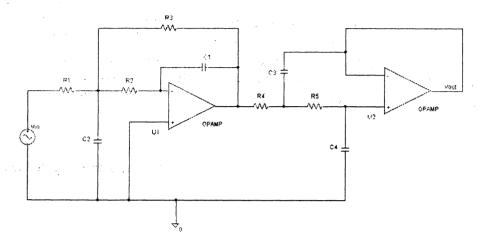

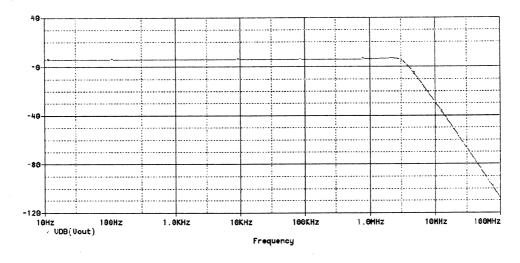

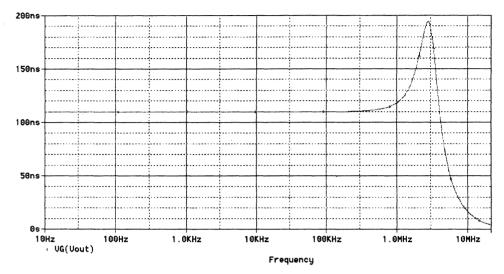

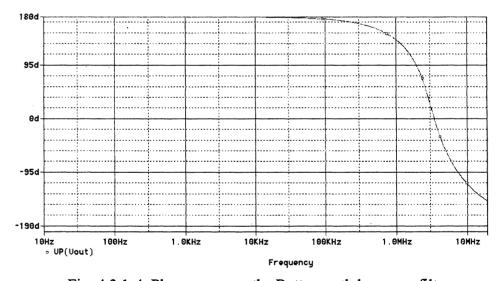

The design problem facing the receiver team is to improve adjacent interferers rejection at the I/Q baseband output of the receiver. To accomplish this, an active fourth-order low-pass Butterworth filter is designed, simulated, implemented, and tested. Of the numerous filter types available, this one is chosen for its gain, high linearity, maximally flat response in the pass-band, and minimal number of components required. The final design uses a Sallen-Key topology and provides 6 dB of gain in the pass-band, with a corner frequency of 3 MHz. A spreadsheet is created for performing the necessary calculations, and *PSpice* is used for simulation of the design. The circuit is realized in hardware, its characteristics extracted with an RF network analyzer, and fine-tuned to meet specifications. The realized circuit obtains 39 dB of attenuation at 15 MHz, meeting the most stringent specifications for the design.

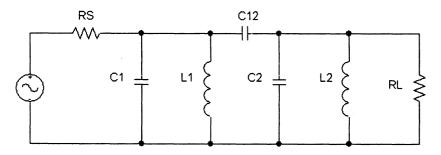

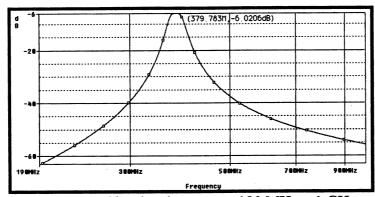

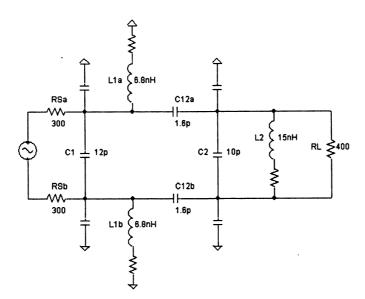

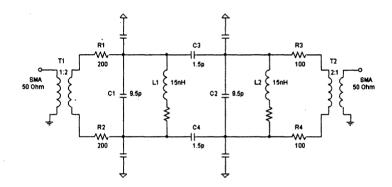

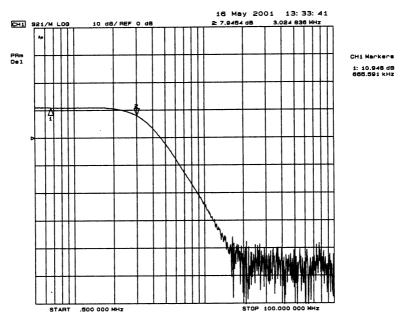

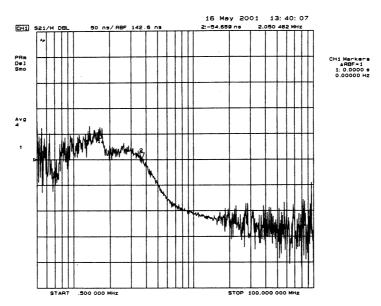

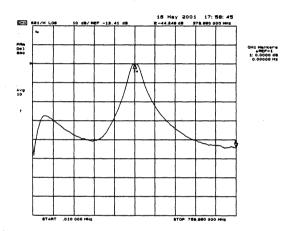

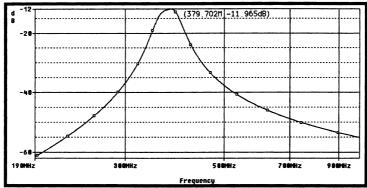

The goal of the transmitter team is to design an IF filter in the transmit path of the radio. The filter must have lower cost and improved performance over the currently used SAW filter, in rejecting harmonics and other spurious signals generated by the quadrature modulation process. To meet the goal, analysis is performed to determine filter specifications and a passive second-order narrowband band-pass Butterworth filter is designed, simulated, and verified in hardware. A capacitive-coupled resonator architecture is chosen for its design characteristics and ease of tuning. A spreadsheet is created to automate design calculations and *PSpice* is used for simulation. Because of the high frequency range involved, special care is taken to account for finite inductor Q and stray capacitance present in the physical circuit. The prototype obtains a 3 dB bandwidth of 35.4 MHz, and 40 to 44 dB of attenuation at 190 and 760 MHz, respectively.

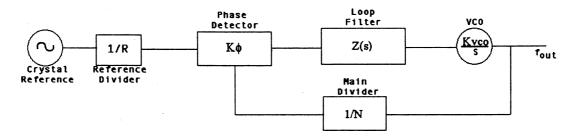

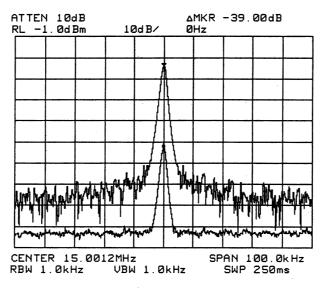

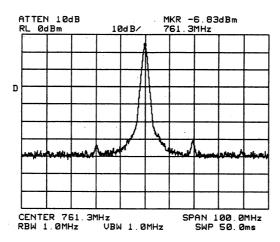

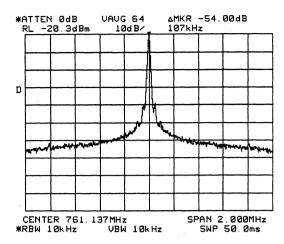

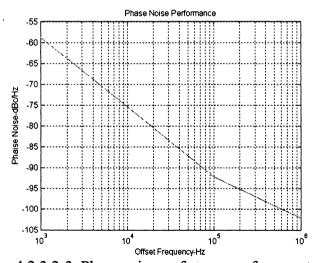

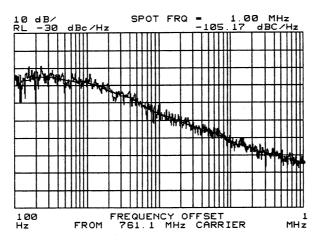

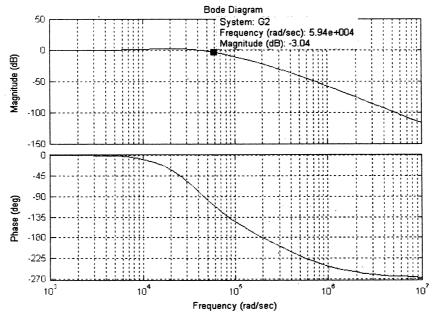

The design problem facing the frequency synthesizer team is to provide four clean local oscillators for the down- and up-conversion of the RF and IF signals in both the receive and transmit paths. To accomplish this goal, phase locked loops are used to produce clean signals at much higher frequencies than obtainable from crystal oscillators. An Integer-N PLL architecture is chosen for its low power consumption, small physical size, and economy. A third-order lead-lag passive low-pass filter is designed because the loop filter is key to generating an output with minimum noise. Key criteria include the amount of phase noise generated, the amount of spurious noise suppressed, and the time taken to lock to a specified frequency. *Matlab* code is written and used to calculate key values and to run simulations for given system specifications. The final loop filter design for the transmitter IFLO features a 1.5 kHz bandwidth, netting -58 dBc/Hz phase noise attenuation and spurious noise at a 1 kHz offset with a settling time of 5 ms.

Keywords – Wireless communications, Wideband Code-Division Multiple Access, Transceiver architecture, Low-pass filter design, Band-pass filter design, PLL design.

# **Table of Contents**

| Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | jе                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Chapter One – Introduction (Karl Doering)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                               |

| 1.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |

| 1.2. A Historical Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| 1.3. A Glossary of Acronyms and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                               |

| Chapter Two – Design and Technical Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

| 2.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                               |

| 2.2. Problem Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                               |

| 2.2.1. Receiver (Steven Gyford)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                               |

| 2.2.2. Transmitter (Michael Wilson)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |

| 2.2.3. Frequency Synthesizer (Oscar Servin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |

| 2.3. Design Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

| 2.3.1. Receiver (Steven Gyford)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| 2.3.2. Transmitter (Michael Wilson)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |

| 2.3.3. Frequency Synthesizer (Heath Deuel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

| 2.3.3.1. Radio Frequency Local Oscillator (RFLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 2.3.3.2. Receive Path – Intermediate Frequency Local Oscillator (Rx-IFLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

| 2.3.3.3. Transmit Path – Intermediate Frequency Local Oscillator (Tx-IFLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| Chapter Three – Method of Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |

| 3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | n                               |

| 3.2. Our Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| 3.2.1. Receiver (Nadim Addus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| 3.2.2. Transmitter (Karl Doering)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |

| 3.2.3. Frequency Synthesizer (Oscar Servin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |

| 3.2.3.1. Integer-N Phase Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

| 3.2.3.2. Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| 3 3 1 Receiver (Steven Guford)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ,<br>7                          |

| 3 3 2 Transmitter (Karl Dogring)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,<br>δ                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| 3.4 Lessons Learned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )<br>()                         |

| 3.4.1 Receiver (Nadim Addus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )<br>N                          |

| 3.4.2. Transmitter (Karl Doering)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>N                          |

| 3.4.3. Frequency Synthesizer (Oscar Servin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )                               |

| 3.2.3.3. Phase Frequency Detector       15         3.2.3.4. Loop Filter       16         3.2.3.5. Voltage Controlled Oscillator       16         3.3. Alternative Approach / Design Trade Off       17         3.3.1. Receiver (Steven Gyford)       17         3.3.2. Transmitter (Karl Doering)       18         3.3.3. Frequency Synthesizer (Oscar Servin)       19         3.4.1. Receiver (Nadim Addus)       20         3.4.2. Transmitter (Karl Doering)       20         3.4.3. Frequency Synthesizer (Oscar Servin)       20 | 6<br>6<br>7<br>7<br>8<br>9<br>0 |

# **Table of Contents (continued)**

| Chapter Four – Evaluation                 |                       |    |

|-------------------------------------------|-----------------------|----|

| 4.1. Introduction                         |                       |    |

| 4.2. Discussion of Results / Test Plan    |                       |    |

| 4.2.1. Receiver (Nadim Addus)             |                       | 21 |

| 4.2.2. Transmitter (Karl Doering)         |                       | 23 |

| 4.2.2.1. Initial Plan                     |                       | 23 |

| 4.2.2.2. Intermediate Trials              |                       | 23 |

| 4.2.2.3. Final Plan                       |                       | 25 |

|                                           | uel and Oscar Servin) |    |

|                                           |                       |    |

| 4 2 3 2 Discussion of Results             |                       | 26 |

| 4.2.3.2. Discussion of Results            |                       | 29 |

| 431 Receiver (Nadim Addus)                |                       | 29 |

| 432 Transmitter (Karl Dogring)            |                       | 33 |

| 133 Frequency Synthesizer (Heath Da       | ual)                  | 35 |

| 4.3.3. Proquency Symmesizer (Tream Det    | wei)                  | 55 |

| Chantas Eiro Administrative (Michael Wile | 1                     |    |

| 5.1. Introduction                         | on)                   | 37 |

| 5.1. Illitoduction                        |                       | 27 |

| 5.2. Cost Analysis                        | •••••••               | 21 |

| 5.3. Organization of the Task             |                       | 30 |

| •                                         |                       |    |

| Chapter Six – Meeting Expectations        |                       | 20 |

| 6.1. Introduction                         | ,                     | 39 |

| 0.2. Design Constraints                   |                       | ンフ |

| 6.2.1. Receiver (Steven Gyford)           |                       | 39 |

| 6.2.2. Transmitter (Michael Wilson)       |                       | 40 |

| 6.2.3. Frequency Synthesizer (Heath Dei   | uel)                  | 41 |

| 6.3. Elements of Design (Steven Gyford)   |                       | 43 |

|                                           |                       |    |

| Chapter Seven – Conclusions               |                       |    |

| 7.1. Introduction                         |                       | 44 |

| 7.1. Introduction                         |                       | 44 |

| 7.2.1. Receiver (Nadim Addus)             |                       | 44 |

| 7.2.2. Transmitter (Michael Wilson)       |                       | 44 |

| 7.2.3. Frequency Synthesizer (Heath Det   | uel and Oscar Servin) | 44 |

| 7.3. User's Manual                        |                       | 45 |

|                                           |                       |    |

# **Table of Contents (continued)**

| Appendix A: Parts List                         | 46 |

|------------------------------------------------|----|

| Appendix B: Equipment List                     |    |

| Appendix C: Software List                      |    |

| Appendix D: Special Resources                  |    |

| Appendix E: Parts Cost Breakdown               |    |

| Appendix F: Matlab Code for Loop Filter Design |    |

| References                                     | 51 |

| Acknowledgement                                | 53 |

# **Chapter One – Introduction**

# 1.1. Introduction

This project involves the analysis of and improvement upon a Wideband Code-Division Multiple Access transceiver. We divide the tasks among ourselves at the block level into three portions: receive, transmit, and frequency synthesis. Each portion is attacked by a team of two EE senior design students at UC Riverside working with an industry engineer from Maxim Integrated Products. After performing preliminary research and analysis to become familiar with the reference architecture and design issues involved, each team works on a particular aspect of the design as described in this paper.

In the remainder of this chapter we give a brief historical perspective followed by a glossary of acronyms and abbreviations we frequently use. Chapter Two introduces the specific design problem of each team, providing a general problem statement followed by precise design specifications. In Chapter Three the method of solution for each team is presented, beginning with an overview of the chosen design solution among a variety of possible solutions. The designs are presented in detail, with the key features and functions of each component emphasized. In Section 3.3 alternative approaches to the design problem and the tradeoffs involved are examined more closely. Chapter Three closes with insight into some of the valuable lessons learned in the design process.

In Chapter Four, each team conducts a thorough evaluation of its design. Results from both *PSpice* simulations and hardware measurements are presented, compared, and contrasted. Both strengths and weaknesses in the design are stated and evaluated with respect to alternative methods of solution available.

Chapter Five deals with key administrative issues, including a complete cost analysis and a description of task organization and scheduling. In Chapter Six, the design constraints are reexamined. Discrepancies in the results from the original design specifications are examined and accounted for, and the corresponding effect on the final outcome is analyzed. The chapter closes with a table addressing elements of design, including economic factors, safety, reliability, aesthetics, ethics, and social impacts.

We conclude in Chapter Seven by discussing the impact of our work and possible future expansions.

# 1.2. A Historical Perspective

Since 1901, when Marconi first transmitted radio signals across the Atlantic Ocean, radio communication has progressed dramatically [14]. Early radio architectures were very simple and could be easily built out of one's garage with a few components. As radio communication became more popular and more and more communication by radio took place, people soon realized that the electromagnetic spectrum is a precious resource which must be shared among all involved. Frequency plans were created, and higher and higher frequency ranges were explored.

Design techniques advanced, and new architectures were developed to handle the problems encountered with higher-frequency designs.

Early radios worked in the kHz range, but today's W-CDMA architecture operates in the GHz range. Simple LC filters cannot be built to select narrow channels at such high frequencies, and techniques such as down-conversion, up-conversion, and intermediate frequencies are required, leading to the superheterodyne architecture commonly used today.

# 1.3. A Glossary of Acronyms and Abbreviations

| ACS adjacent channel selectivity  Atten added spurious attenuation due to R3 and C3  CDMA code-division multiple access  dBc decibels relative to carrier  dBm decibels referenced to one milliwatt  DSP digital signal processor  Fcomp comparison frequency  FDD frequency division duplex  Fout output frequency of the VCO  Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  Icp phase detector / charge pump gain  IF intermediate frequency local oscillator  IP3 third-order intercept  KVCO VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  Wc-CDMA wideband code-division multiple access                                                                                        | 3GPP             | Third Generation Partnership Project       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------|

| Atten added spurious attenuation due to R3 and C3 CDMA code-division multiple access  dBc decibels relative to carrier  dBm decibels referenced to one milliwatt  DSP digital signal processor  Fcomp comparison frequency  FDD frequency division duplex  Fout output frequency of the VCO  Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  Icp phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP3 third-order intercept  Kvco VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency  RSF radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator                                                   |                  |                                            |

| CDMA code-division multiple access  dBc decibels relative to carrier  dBm decibels referenced to one milliwatt  DSP digital signal processor  F <sub>comp</sub> comparison frequency  FDD frequency division duplex  F <sub>out</sub> output frequency of the VCO  F <sub>ref</sub> crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Meps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx  receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator              |                  |                                            |

| dBc decibels relative to carrier dBm decibels referenced to one milliwatt  DSP digital signal processor  F <sub>comp</sub> comparison frequency  FDD frequency division duplex  F <sub>out</sub> output frequency of the VCO  F <sub>ref</sub> crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator |                  |                                            |

| dBm decibels referenced to one milliwatt  DSP digital signal processor  F_comp comparison frequency  FDD frequency division duplex  F_out output frequency of the VCO  F_ref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I_cp phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP3 third-order intercept  K_VCO VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                       |                  |                                            |

| DSP digital signal processor  Fcomp comparison frequency  FDD frequency division duplex  Fout output frequency of the VCO  Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  Icp phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP3 third-order intercept  Kvco VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  True closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                         |                  |                                            |

| Foomp comparison frequency  FDD frequency division duplex  Fout output frequency of the VCO  Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  True closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                   |                  |                                            |

| FDD frequency division duplex  Fout output frequency of the VCO  Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                               |                  |                                            |

| Fout output frequency of the VCO Fref crystal reference frequency I/Q in-phase and quadrature IC integrated circuit  I_{cp} phase detector / charge pump gain IF intermediate frequency IFLO intermediate frequency local oscillator IP3 third-order intercept K_VCO VCO gain (tuning sensitivity) LNA low-noise amplifier LO local oscillator Mcps million chips per second N N divider value PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                        | Fcomp            |                                            |

| Fref crystal reference frequency  I/Q in-phase and quadrature  IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                |                  |                                            |

| I/Q in-phase and quadrature IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain IF intermediate frequency IFLO intermediate frequency local oscillator IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                      |                  |                                            |

| IC integrated circuit  I <sub>cp</sub> phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP <sub>3</sub> third-order intercept  K <sub>VCO</sub> VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                               |                  |                                            |

| Icp phase detector / charge pump gain  IF intermediate frequency  IFLO intermediate frequency local oscillator  IP3 third-order intercept  Kvco VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |                                            |

| IF intermediate frequency IFLO intermediate frequency local oscillator IP3 third-order intercept K <sub>VCO</sub> VCO gain (tuning sensitivity) LNA low-noise amplifier LO local oscillator Mcps million chips per second N N divider value PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                            |

| IFLO intermediate frequency local oscillator IP <sub>3</sub> third-order intercept K <sub>VCO</sub> VCO gain (tuning sensitivity) LNA low-noise amplifier LO local oscillator Mcps million chips per second N N divider value PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                            |

| IP3       third-order intercept         K <sub>VCO</sub> VCO gain (tuning sensitivity)         LNA       low-noise amplifier         LO       local oscillator         Mcps       million chips per second         N       N divider value         PCB       printed circuit board         PFD       phase frequency detector         PLL       phase locked loop         Q       quality factor         R       R divider value         RF       radio frequency         RFLO       radio frequency local oscillator         RMS       root mean square (reference to phase noise)         Rx       receive         SAW       surface acoustic wave (filter)         SMT       surface-mount technology         Tx       transmit         TXCO       temperature-compensated crystal oscillator         VCO       voltage-controlled oscillator         Wc       true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                       |                  |                                            |

| Kvco VCO gain (tuning sensitivity)  LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IFLO             | intermediate frequency local oscillator    |

| LNA low-noise amplifier  LO local oscillator  Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $IP_3$           |                                            |

| LO local oscillator Mcps million chips per second N N divider value PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | K <sub>VCO</sub> | VCO gain (tuning sensitivity)              |

| Mcps million chips per second  N N divider value  PCB printed circuit board  PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LNA              | low-noise amplifier                        |

| PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LO               | local oscillator                           |

| PCB printed circuit board PFD phase frequency detector PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mcps             | million chips per second                   |

| PFD phase frequency detector  PLL phase locked loop  Q quality factor  R R divider value  RF radio frequency  RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | N                | N divider value                            |

| PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PCB              | printed circuit board                      |

| PLL phase locked loop Q quality factor R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PFD              | phase frequency detector                   |

| R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PLL              |                                            |

| R R divider value RF radio frequency RFLO radio frequency local oscillator RMS root mean square (reference to phase noise) Rx receive SAW surface acoustic wave (filter) SMT surface-mount technology Tx transmit TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q                | quality factor                             |

| RFLO radio frequency local oscillator  RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  Wc true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                                            |

| RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RF               | radio frequency                            |

| RMS root mean square (reference to phase noise)  Rx receive  SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RFLO             | radio frequency local oscillator           |

| SAW surface acoustic wave (filter)  SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RMS              |                                            |

| SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Rx               | receive                                    |

| SMT surface-mount technology  Tx transmit  TXCO temperature-compensated crystal oscillator  VCO voltage-controlled oscillator  w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SAW              | surface acoustic wave (filter)             |

| TXCO temperature-compensated crystal oscillator VCO voltage-controlled oscillator w <sub>c</sub> true closed-loop bandwidth (rad/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                                            |